#### **Analog and Digital Electronics**

Prepared by :

N Naresh Chary Assistant Professor Department of ECE NRCM,Hyderabad

#### **UNIT - I Diodes and applications**

#### Atomic Structure

- An atom is composed of :

- •Nucleus ( which contains positively charged protons and neutral neutrons)

- •Electrons (which are négative charged and that orbit the nucleus)

#### **Valence Electrons**

- •Electrons are distributed in various shells at different distances from nucleus

- Electron energy increases as shell radius increases.

- •Electrons in the outer most Shell are called as valence electrons

- •Elements in the period table are grouped according to the number of valence electrons.

#### **Valence Electrons**

| Table 1.1 | A portion of th | ne periodic |

|-----------|-----------------|-------------|

| table     |                 |             |

| ш  | IV      | V |

|----|---------|---|

| В  | С       |   |

| Al | C<br>Si | Р |

| Ga | Ge      | A |

# **Elemental/Compound Semiconductor**

# Silicon (Si) and Germanium (Ge) are in group IV, and are elemental semiconductors Galium arsenide (GaAs) is a goup III-V compound semiconductor

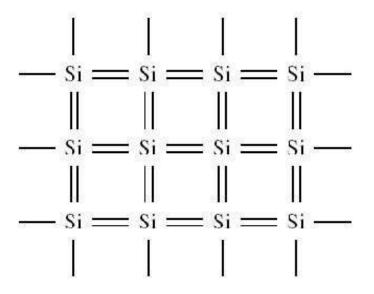

## **Silicon Crystal**

→ At 0°K, each electron is in its lowest possible energy state, and each covalent bounding position is filled.

• $\rightarrow$ If a small electric field is applied, the electrons will not move  $\rightarrow$  silicon is an **insulator**

# Silicon Atom Diagram at 0°K

Two-dimensional representation of the silicon crystal at T = 0 °K

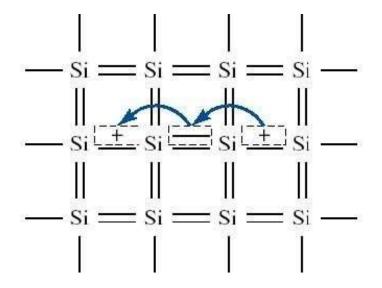

#### **Intrinsic Silicon**

- →If the temperature increases, the valence electrons will gain some thermal energy, and breaks free from the covalent bond → It leaves a positively charged hole

- → In order to break from the covalent bond, a valence electron must gain a minimun energy *Eg*: Bandgap energy

# Silicon Atom Diagram at Ambiant Temp Si = Si = Si -Si 🚃 si + si = si = si - siSi = Si = Si = Si

The breaking of a covalent bond for T > 0 K

# **Insulators & Conductors**

- •Materials that have large bandgap energies (in the range of 3 to 6 electron-volts (eV)) are **insulators**, because at room temperature, essentially no free electron exists in the material

- •Materials that contain very large number of free electrons at room temperature are **conductors**

#### **Semiconductors**

- •→ In a semiconductor, the bandgap energy is in the order of 1 eV. The net flow of free electrons causes a current.

- •→ In a semiconductor, two types of charged particles contribute to the current: the negatively charged electrons and the positively charged holes

#### Movement of Holes Movement of Holes

A two- dimensional representation of the silicon crystal showing the movement of the positively charged hole

#### Semiconductor Constants

- •The concentration of electrons and holes directly influence the magnitde of the current

- In an intrinsic semiconductor (a single crystal semiconductor) the densities of holes and electrons are equal.

# *ni:* intrinsic carrier concentration for free electrons (same for holes)

$$n_i = BT^{3/2} e^{\left(\frac{-E_g}{2kT}\right)}$$

B: constant related to specific semiconductor material Eg: Bandgap energy (eV) T: Temperature (°K) K: Boltzman Constant (86 E-06 eV/°K)

#### **Semiconductor Constants**

#### Semiconductor constants

| Material                | $E_g$ (eV) | $B ({\rm cm}^{-3} {}^{\circ}{\rm K}^{-3/2})$ |

|-------------------------|------------|----------------------------------------------|

| Silicon (Si)            | 1.1        | $5.23 \times 10^{15}$                        |

| Gallium arsenide (GaAs) | 1.4        | $2.10 \times 10^{14}$                        |

| Germanium (Ge)          | 0.66       | $1.66 \times 10^{15}$                        |

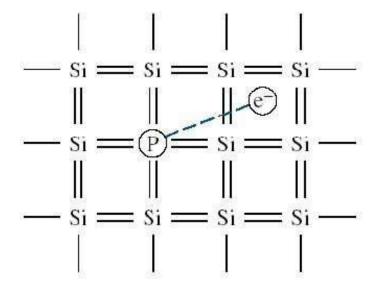

#### Extrinsic Semiconductor / Doping

- •The electron or hole concentration can be greatly increased by adding controlled amounts of certain impurities

- •For silicon, it is desirable to use impurities from the group III and V.

- •An N-type semiconductor can be created by adding phosphorus or arsenic

#### Extrinsic Semiconductor / Doping

- The phosphorus (group V) atom is called **donor impurity** because it donates an electron that is free to move

- •The boron (group **III**) has accepted a valence electron (or donated a hole), it is therefore called **acceptor impurity**

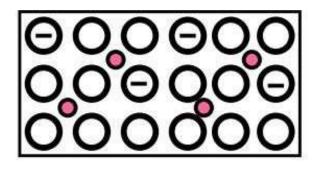

#### N-Type Semiconductor

Two-dimensional representation of a silicon lattice doped with a phosphorus atom

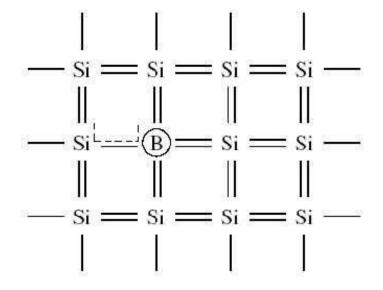

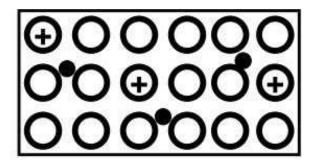

#### **P-Type Semiconductor**

Two-dimensional representation of a silicon lattice doped with a boron atom

#### Introduction to Semiconductor Devices

**Semiconductor p-n junction diodes**

# p-n junction formation

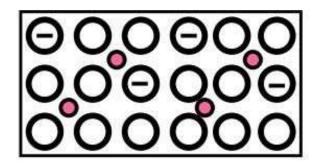

#### p-type material

Semiconductor material doped with **acceptors**.

Material has high hole concentration

Concentration of free electrons in p-type material is very low.

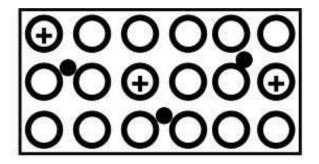

#### n-type material

Semiconductor material doped with **donors**.

Material has high concentration of free electrons.

Concentration of holes in n-type material is very low.

# p-n junction formation

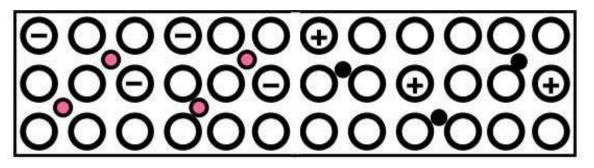

#### p-type material :

Contains NEGATIVELY charged acceptors (immovable) and POSITIVELY charged holes (free).

Total charge = 0

#### n-type material :

Contains POSITIVELY charged donors (immovable) and NEGATIVELY charged free electrons.

Total charge = 0

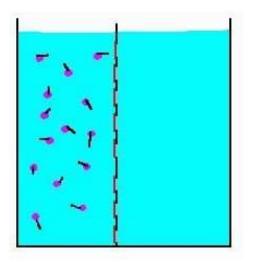

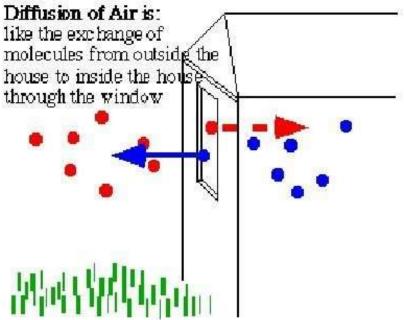

#### Diffusion

A substance, the purple dots, in solution. A membrane prevents movement of the water and the molecules from crossing from one side of the beaker to the other.

Now that the gates have been opened, the random movements of the molecules have caused, overtime, the number of molecules to be equal on the two sides of the barrier.

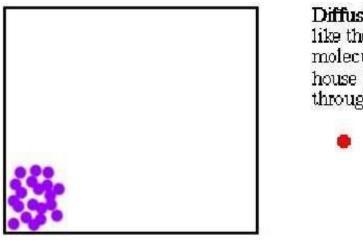

#### Diffusion

As a result of diffusion, the molecules or other free particles distribute uniformly over the entire volume

# **p-n junction formation**

What happens if n- and p-type materials are in close contact?

Being free particles, **electrons** start diffusing from n-type material into p-material

Being free particles, holes, too, start diffusing from p-type material into n-material

Have they been NEUTRAL particles, eventually all the free electrons and holes had uniformly distributed over the entire compound crystal.

However, every electrons transfers a negative charge (-q) onto the p-side and also leaves an uncompensated (+q) charge of the donor on the n-side.

Every hole creates one positive charge (q) on the n-side and (-q) on the p-side

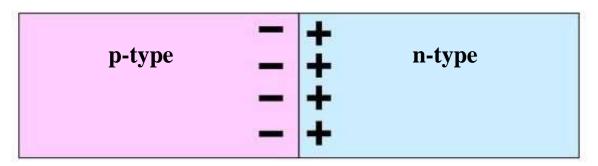

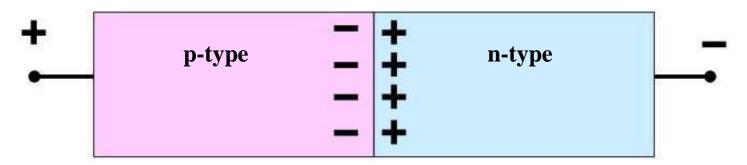

### **p-n junction formation**

What happens if n- and p-type materials are in close contact?

Electrons and holes remain staying close to the p-n junction because negative and positive charges attract each other. Negative charge stops electrons from further diffusion

Positive charge stops holes from further diffusion

The diffusion forms a dipole charge layer at the p-n junction interface.

There is a "built-in" VOLTAGE at the p-n junction interface that prevents penetration of electrons into the p-side and holes into the n-side.

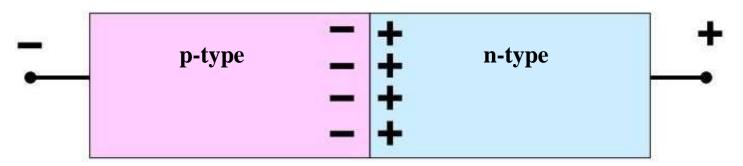

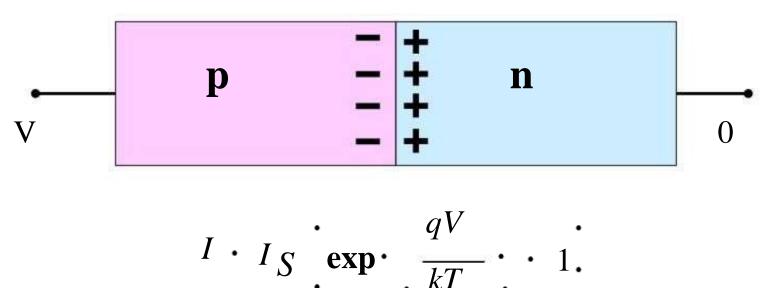

#### **p- n junction current - voltage** characteristics

What happens when the voltage is applied to a p-n junction?

The polarity shown, attracts holes to the left and electrons to the right.

According to the **current continuity law,** the current can **only** flow if all the charged particles move forming a closed loop

However, there are very few holes in n-type material and there are very few electrons in the p-type material.

There are very few carriers available to support the current through the junction plane

For the voltage polarity shown, the current is nearly zero

#### **p- n junction current - voltage characteristics**

What happens if voltage of opposite polarity is applied to a p-n junction?

The polarity shown, attracts electrons to the left and holes to the right.

There are plenty of electrons in the n-type material and plenty of holes in the p-type material.

There are a lot of carriers available to cross the junction.

When the voltage applied is lower than the built-in voltage, the current is still nearly zero

When the voltage exceeds the built-in voltage, the current can flow through the p-n junction

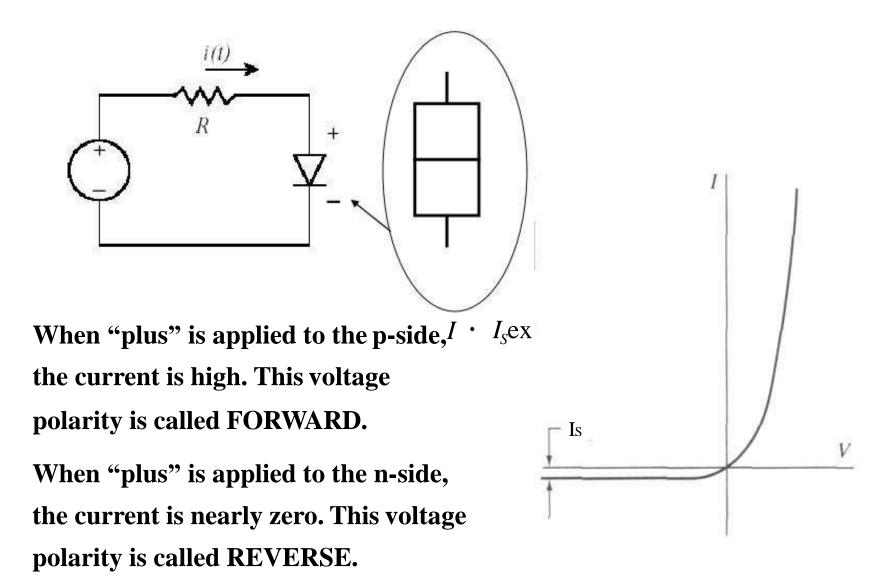

#### **Diode current - voltage (I-V) characteristics**

Semiconductor diode consists of a p-n junction with two contacts attached to the p- and n- sides

Is is usually a very small current, Is  $\approx 10$ -17 ... 10-13 A

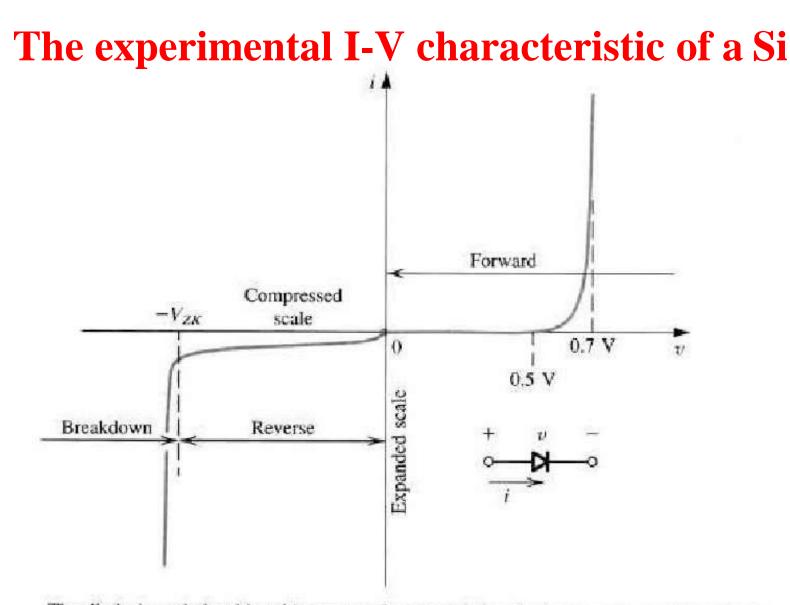

When the voltage V is negative ("reverse" polarity) the exponential term  $\approx$  -1; The diode current is  $\approx$  Is (very small).

When the voltage V is positive ("forward" polarity) the exponential term increases rapidly with V and the current is high.

# Graphing the I-V characteristics of electronic component The I-V plot represents is the dependence of the current I through the component on the voltage V across it. Resistor $V \cdot I \cdot R; \cdot I \cdot \cdot \frac{1}{R} \cdot V$ I = V / R; $\mathbf{R} = \mathbf{V}/\mathbf{I}$ R DI tg(a) = 1/Rа

The I-V characteristic of the resistor

The diode i-v relationship with some scales expanded and others compressed in order to reveal details.

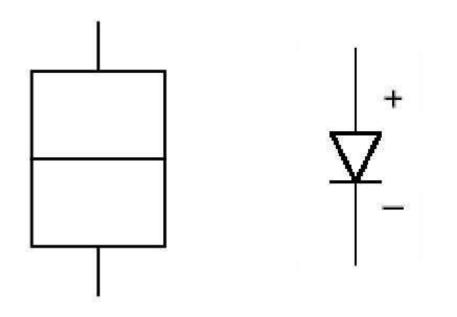

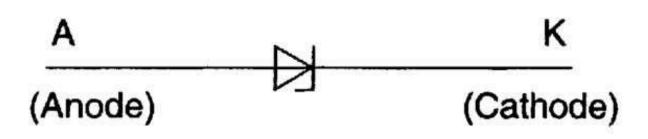

#### p-n diode circuit notation

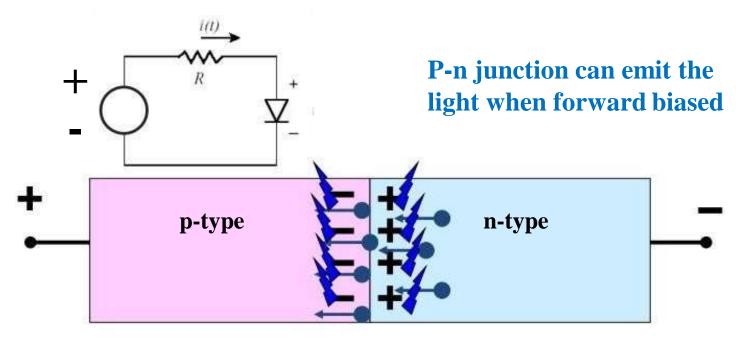

#### p-n diode applications Light emitters

Electrons drift into p-material and find plenty of holes there. They "RECOMBINE" by filling up the "empty" positions.

Holes drift into n-material and find plenty of electrons there. They also "RECOMBINE" by filling up the "empty" positions.

The energy released in the process of "annihilation" produces PHOTONS - the particles of light

#### **Negative resistance devices**

- •It is a device which exhibits a negative incremental resistance over a limited range of V-I characteristic.

- It is of two types :-

- 1. **Current controllable type :** V-I curve is a multi valued function of voltage and single valued function of current .eg:- UJT, p-n-p-n diode

- 2. Voltage controllable type : V-I curve is a multi valued function of current and single valued function of voltage. eg:- SCS, Tunnel diode

#### **TUNNEL DIODE (Esaki Diode)**

- It was introduced by Leo Esaki in 1958.

- Heavily-doped p-n junction

- Impurity concentration is 1 part in 10^3 as compared to 1 part in 10^8 in p-n junction diode

- •Width of the depletion layer is very small (about 100 A).

- It is generally made up of Ge and GaAs.

- It shows tunneling phenomenon.

- Circuit symbol of tunnel diode is :

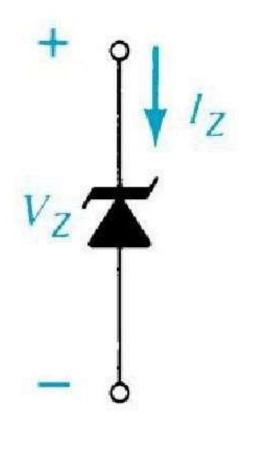

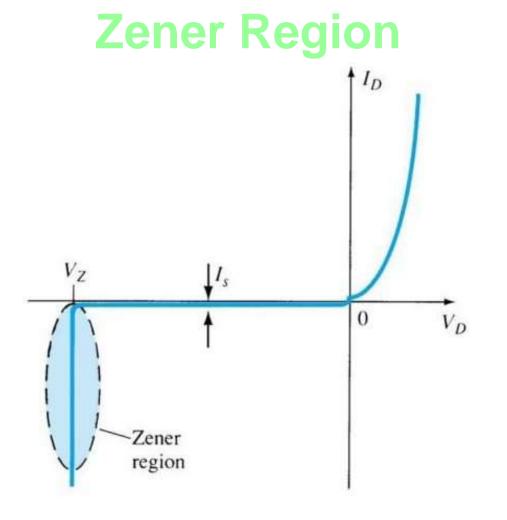

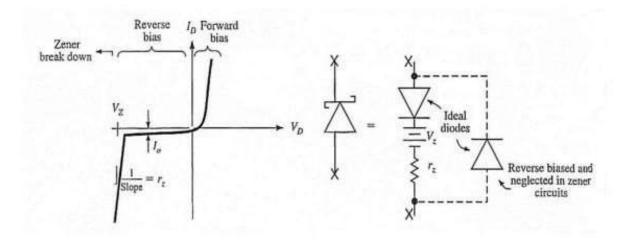

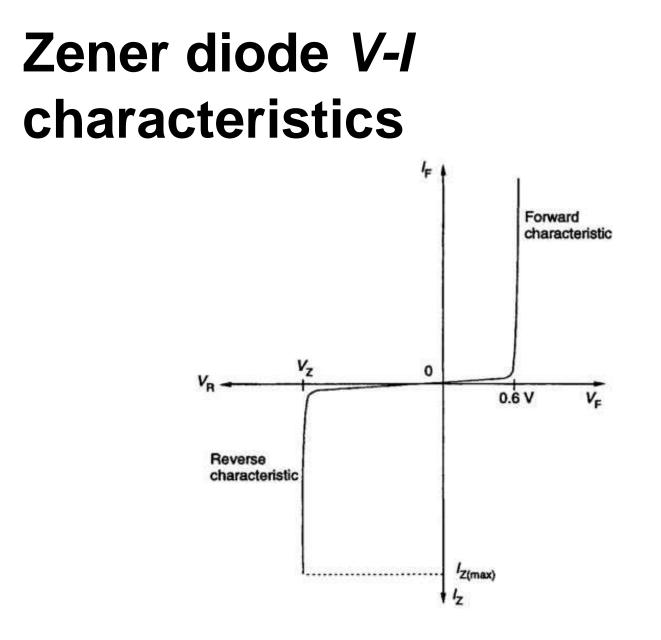

### **Zener Diode**

(a)

•A Zener is a diode operated in reverse bias at the Peak Inverse Voltage (PIV) called the Zener Voltage (Vz).

•Common Zener Voltages: 1.8V to 200V

The diode is in the reverse bias condition.

At some point the reverse bias voltage is so large the diode breaks down.

The reverse current increases dramatically.

This maximum voltage is called *avalanche breakdown voltage* and the current is called *avalanche current*.

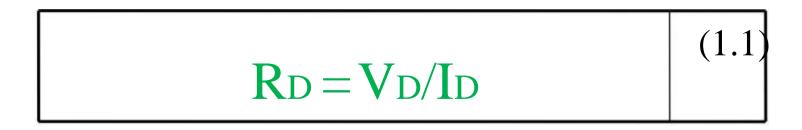

### **Resistance Levels**

Semiconductors act differently to DC and AC currents. There are 3 types of resistances.

- DC or Static Resistance

- AC or Dynamic Resistance

- Average AC Resistance

• DC or Static Resistance

•The resistance of a diode at a particular operating point is called the dc or static resistance diode. It can be determined using equation (1.1):

#### **Example : DC or Static Resistance - refer Figure 1.1**

| Ideal diode        |       |              | Si diode |       |              |

|--------------------|-------|--------------|----------|-------|--------------|

| I <sub>D</sub> (A) | VD(V) | $R_D(\cdot)$ | Id(A)    | VD(V) | $R_D(\cdot)$ |

| 20m                | 0     | 0            | 20m      | 0.8   | 40           |

| 2m                 | 0     | 0            | 2m       | 0.5   | 250          |

dc resistance of forward-bias region decrease when higher currents and voltage.

| Ideal diode        |       |              | Si diode |       |       |

|--------------------|-------|--------------|----------|-------|-------|

| I( <sub>D</sub> A) | VD(V) | $R_D(\cdot)$ | ID(A)    | VD(V) | Rd(·) |

| 0                  | -10   | •            | -2•      | -10   | 5M    |

•dc resistance of reverse-bias region, its open-circuit equivalent.

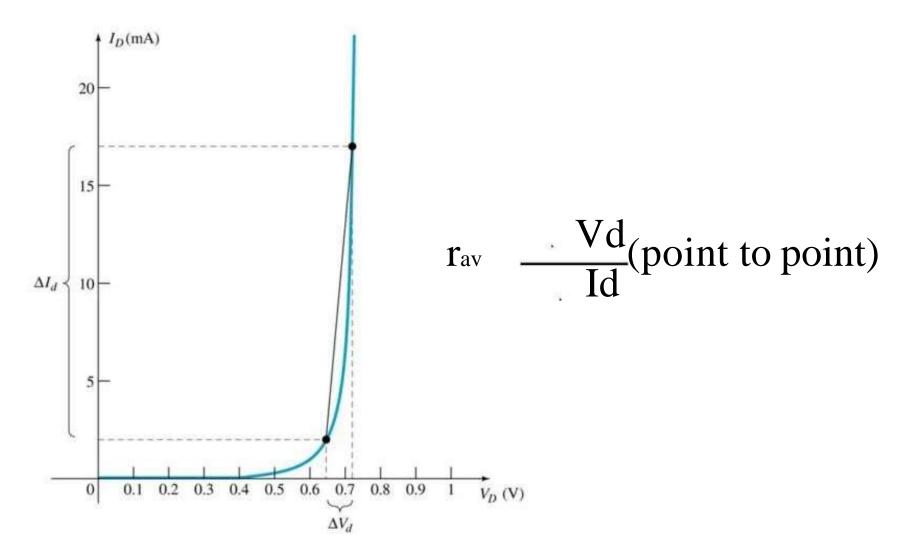

#### • AC or Dynamic Resistance

•Static resistance is using dc input. If the input is sinusoidal the scenario will be change.

•The varying input will move instantaneous operating point UP and DOWN of a region.

• Thus the specific changes in current and voltage is obtained. It can be determined using equation (1.2)

$$\mathbf{r}_{\rm d} = \Delta \mathbf{V}_{\rm D} / \Delta \mathbf{I}_{\rm D} \tag{1.2}$$

•Average AC Resistance

AC resistance can be determined by picking 2 points on the characteristic curve developed for a particular circuit.

### Rectifier

A rectifier is an electrical device that converts alternating current (AC), which periodically reverses direction, to direct current (DC), which is in only one direction, a process known as rectification.

### **Power Supply Circuits**

- To achieve its purpose a power supply must:

- Step down the voltage supplied;

- Convert ac to dc by rectifying the ac.

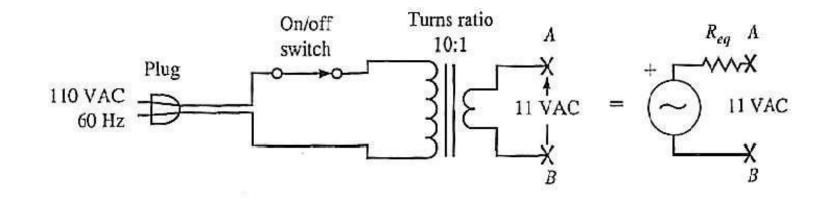

- •A transformer is used to step down the magnitude of the voltages from the wall receptacle.

### Transformer

• A transformer consists of two coils of wire on a common iron core. The voltages on these two coils are related by the *turns ratio*, which is the ratio of the number of turns of wire in the secondary coil to that in the primary coil.

### **RMS Values**

- •Note that the 110-120 volts and 220-240 volts are RMS values.

- •The actual amplitude of that sinusoidal signal is a factor of  $\sqrt{2}$  larger.

### **Types of Rectifiers**

Half wave Rectifier

Full wave Rectifier

Bridge Rectifier

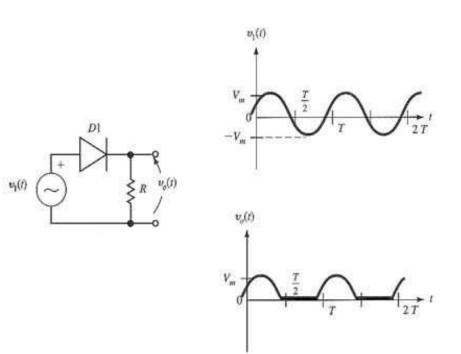

### Half wave Rectifier

In half wave rectification, either the positive or negative

half of the AC wave is passed, while the other

half is blocked.

Because only one half of the input waveform reaches

the output, it is very inefficient if used for power

transfer.

### **Half-wave Rectification**

- Simplest process used to convert ac to dc.

- •A diode is used to clip the input signal excursions of one polarity to zero.

### **Half wave Rectification**

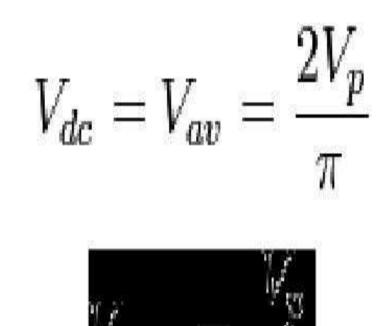

### **Output dc voltage calculation**

The output DC voltage of a half wave rectifier can be

calculated with the following two ideal equations

$$V_{dc} = \frac{V_{peak}}{\pi}$$

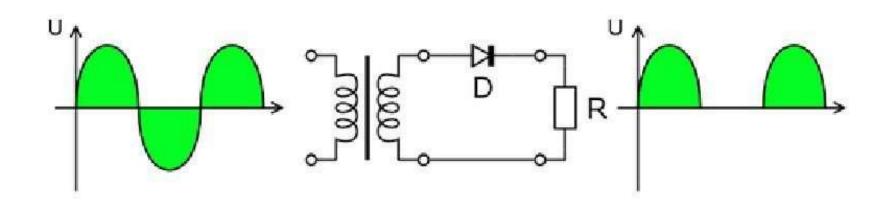

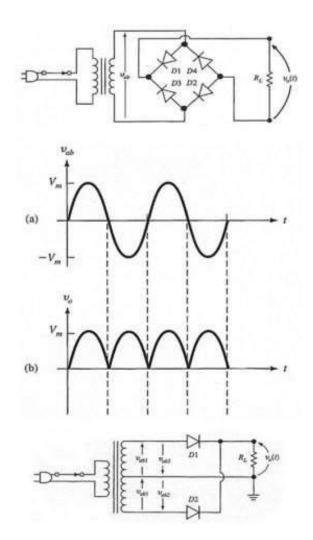

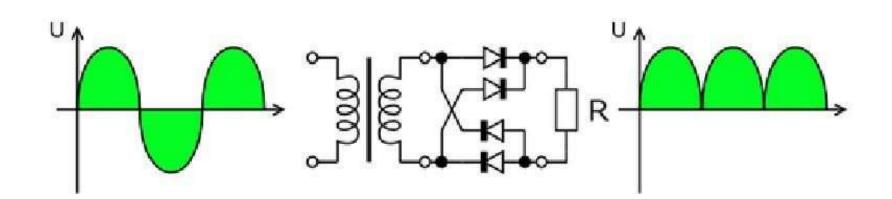

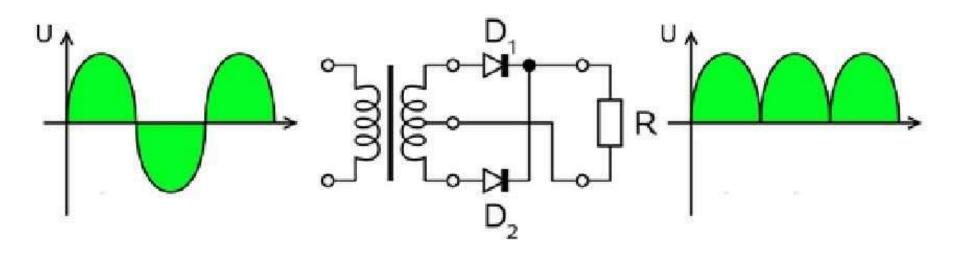

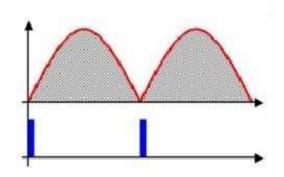

### **Full wave rectifier**

A full-wave rectifier converts the whole of the input waveform

to one of constant polarity (positive or negative) at its

- output. Full-wave rectification converts both polarities of

- the input waveform to DC (direct current), and is more

efficient.0

### **Full-wave Rectification**

• The output of a fullwave rectifier is driven by both the positive and negative cycles of the sinusoidal input, unlike the half-wave rectifier which uses only one cycle.

# Full wave rectifier working animation

### **Full wave rectification**

In a circuit with a non - center tapped transformer, four

diodes are required instead of the one needed for

half- wave rectification.

For single-phase AC, if the transformer is centertapped,

then two diodes back-to-back(i.e. anodes-to-

anode or cathode-to-cathode) can form a full-

wave rectifier.

## Full wave rectifier using 4 diodes

## Full wave rectifier using transformer and 2 diodes

#### ideal single phase full wave rectifier can be calculated as: The average and root-mean-square output voltages of an

### Output voltage of the full waverectifier Animation

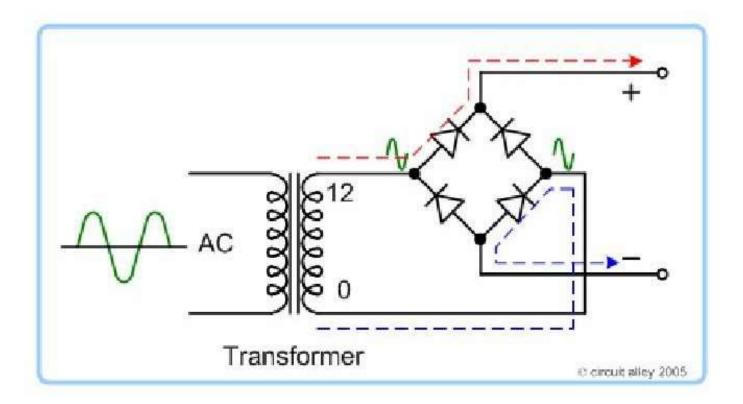

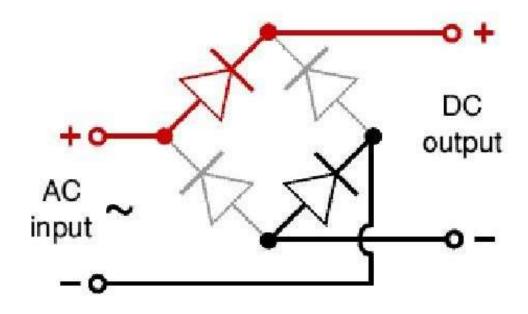

### **Bridge rectifier**

A bridge rectifier makes use of four diodes in a bridge

arrangement to achieve full-wave rectification.

### **Bridge rectifier working animation**

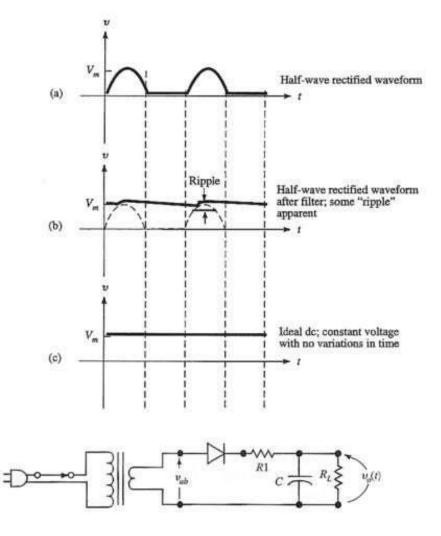

### Filtering

- •Process used to smooth out the output of the rectifier circuit.

- One of the most common filter is the RC network.

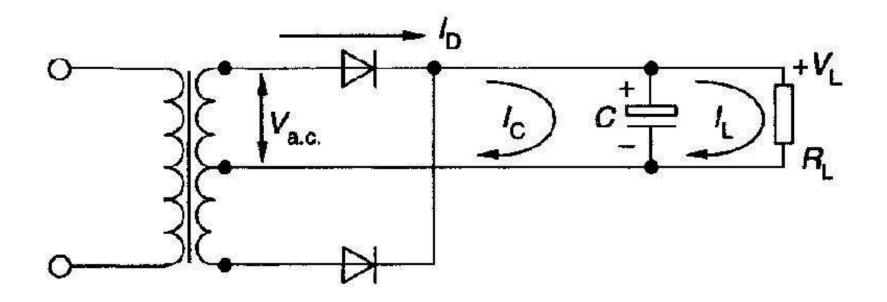

#### Full-wave centre-tap rectifier and capacitor filter with load connected

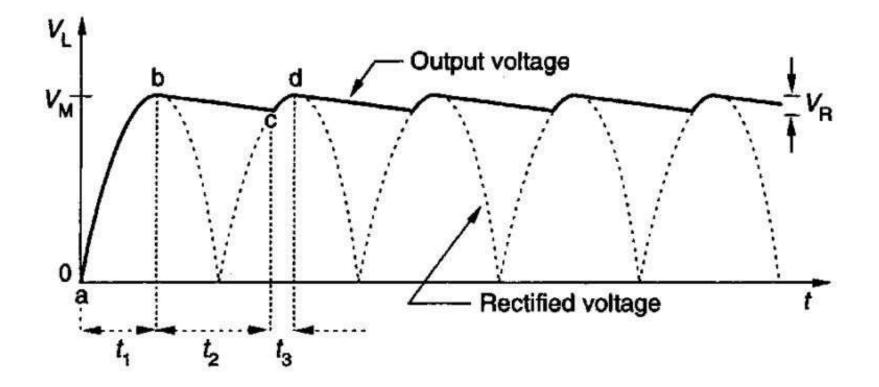

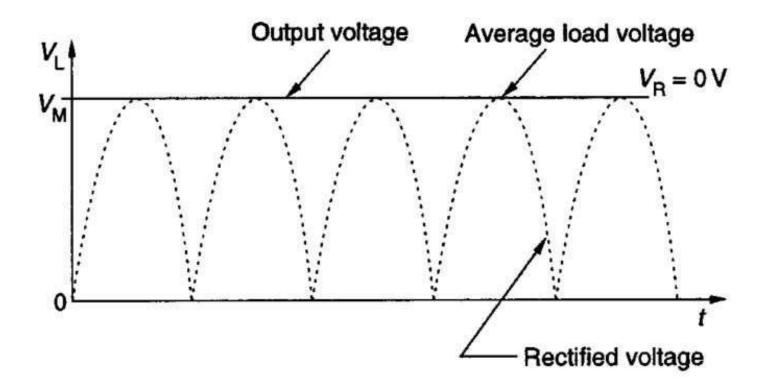

## Capacitor filter output waveforms with load connected

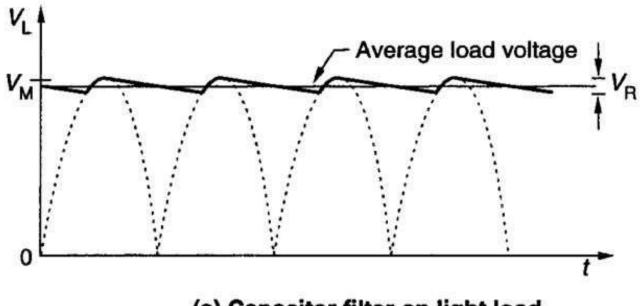

## Effect of load on the output of a capacitor filter circuit

(a) Capacitor filter on light load

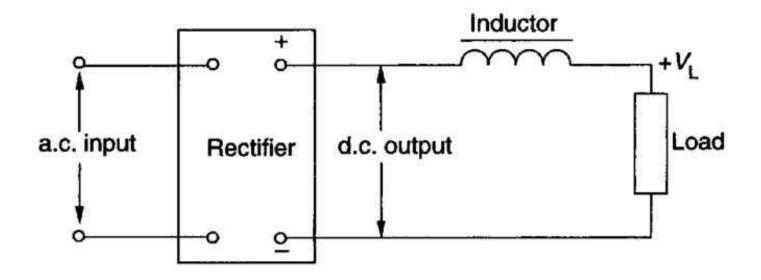

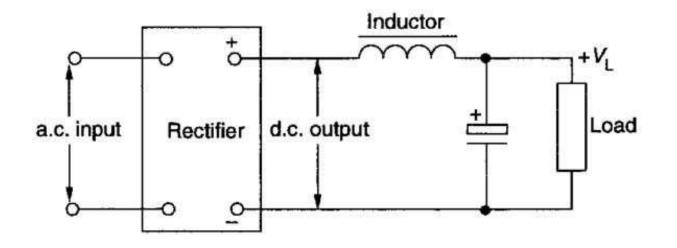

### **Inductor filter**

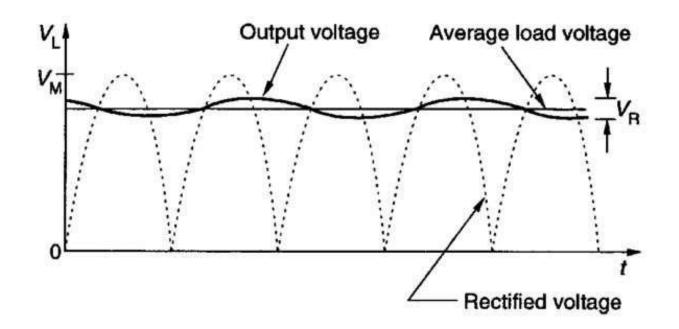

# Inductor filter output voltage waveforms

# Choke input filter (L-section filter)

# Choke input filter load voltage waveforms

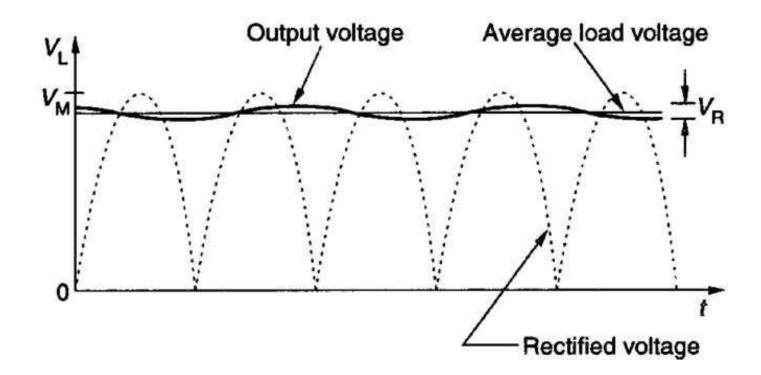

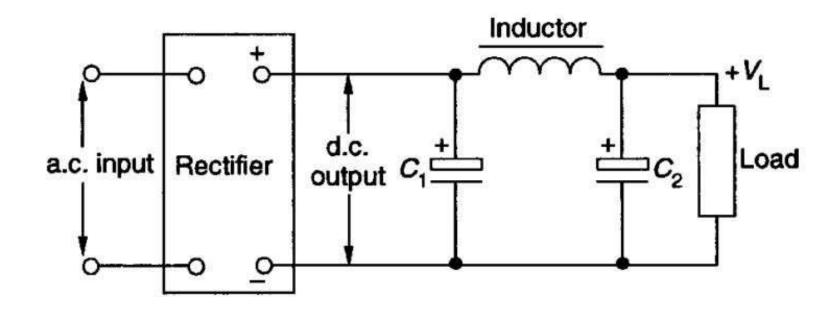

### $\pi$ -type filter

# $\pi$ -type filter output voltage waveforms

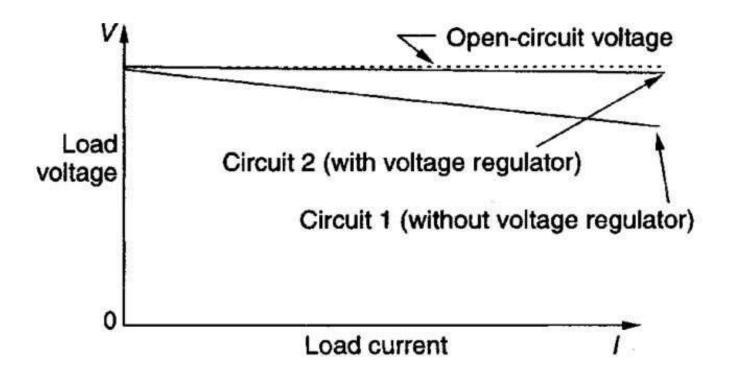

#### Load characteristics for circuits with and without voltage regulators

#### **Zener Diode**

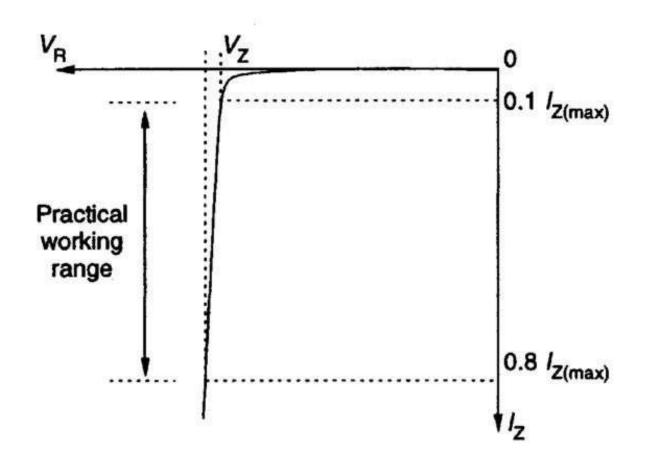

•Analyzing a diode operating in the reverse bias region will show that the current through it remains essentially constant until the *breakdown voltage*, also called the *avalanche* or *zener breakdown voltage*, is reached. At this point the current will increase very rapidly for a small voltage change.

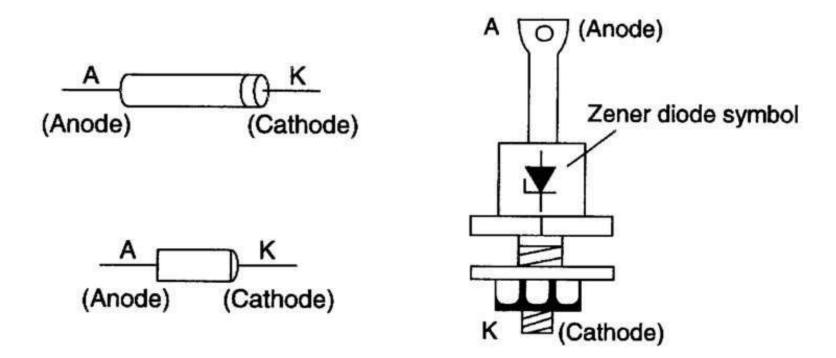

# Zener diode terminal identification

# Zener diode reverse-characteristic working range of currents

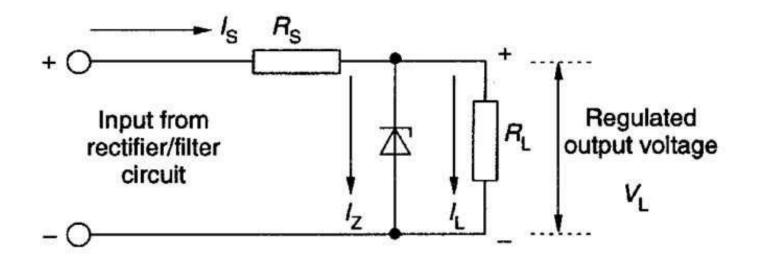

## Zener diode shunt regulator

# **Voltage Regulation**

•This characteristic of the zener diode is very useful for voltage regulation circuits. The zener diode provides an effective way to clamp or limit the voltage at a relatively constant value thus creating a voltage regulation capability.

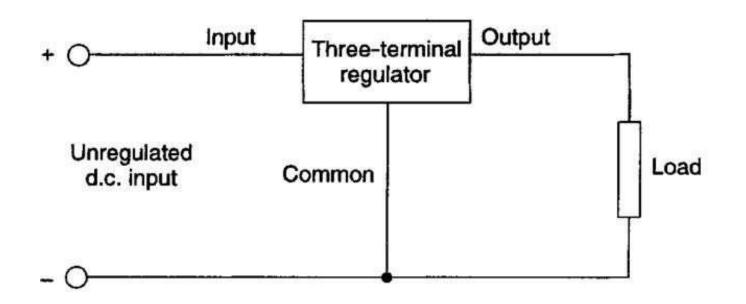

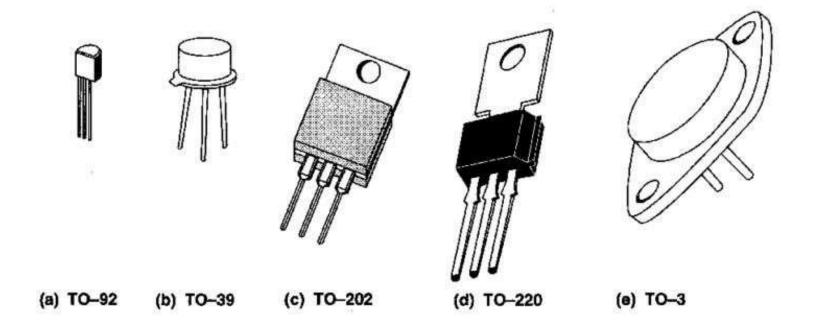

# Three-terminal integrated circuit regulator—basic circuit

## Three-terminal regulator case styles

#### Three-terminal regulator connections positive and negative regulators

1

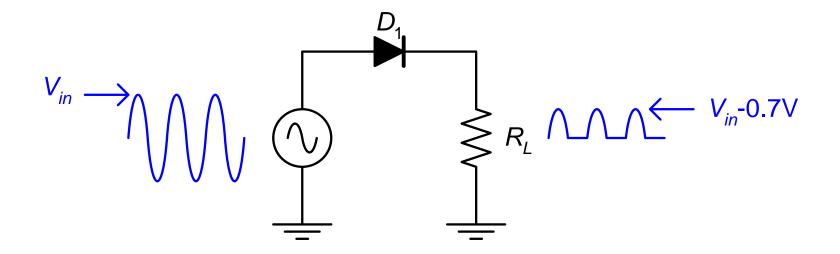

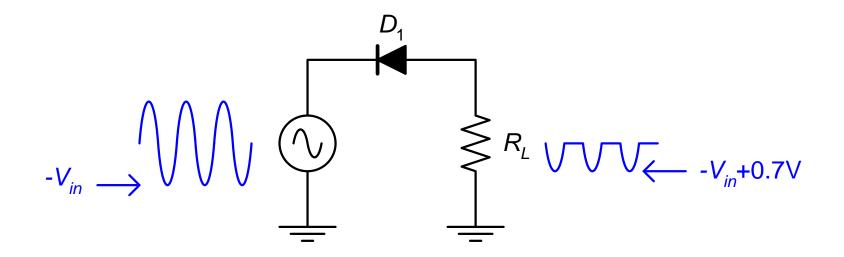

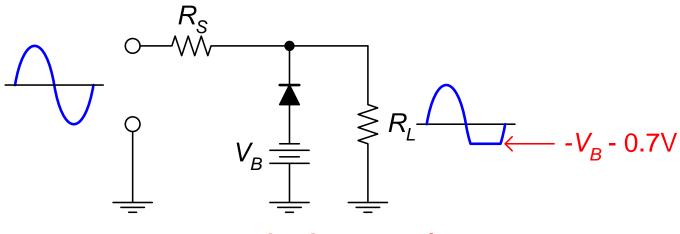

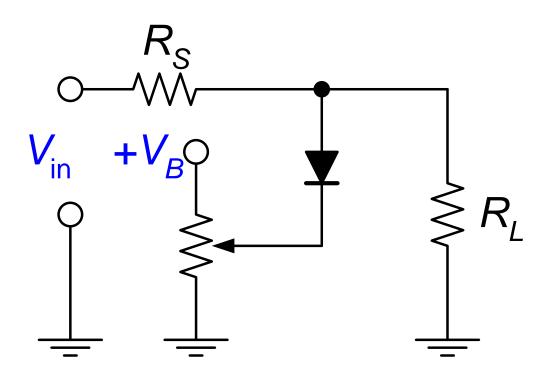

#### **Clipper (limiter) circuits. (1)**

#### Negative series clipper.

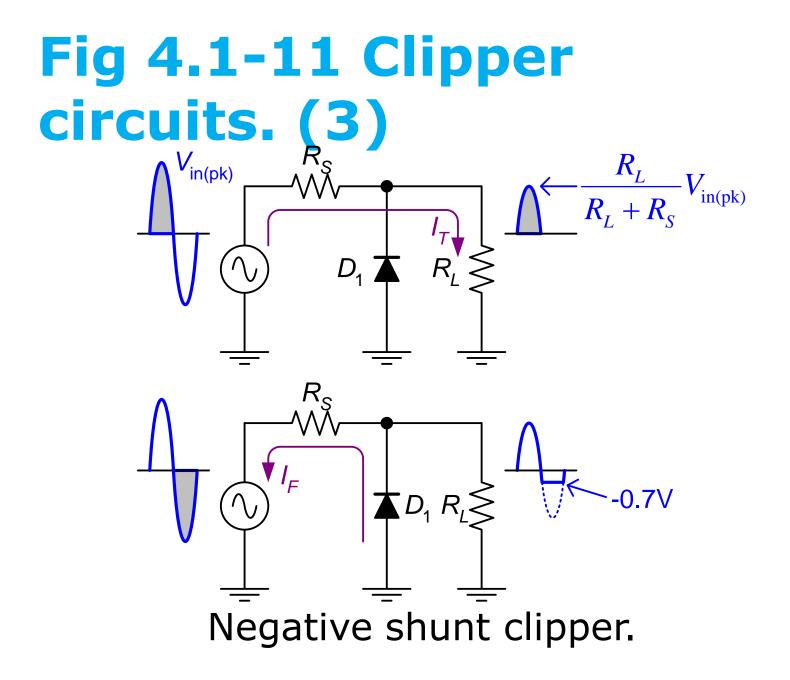

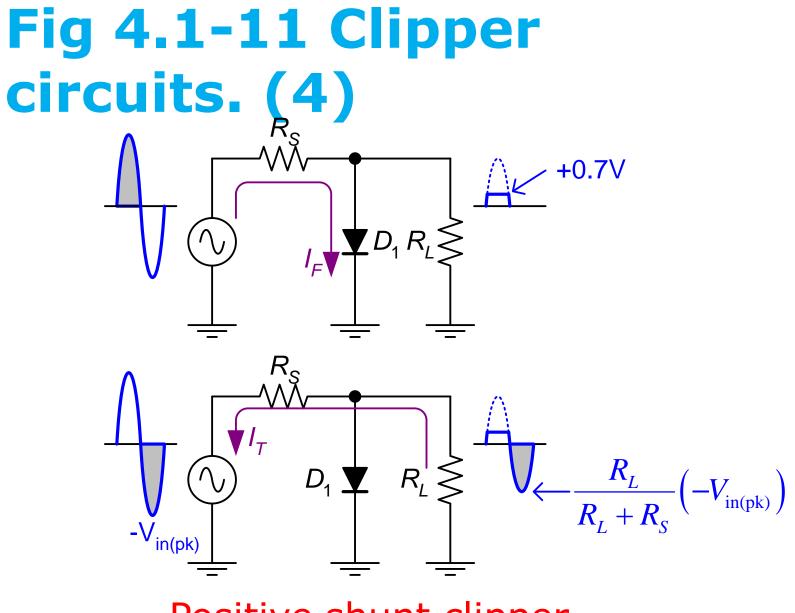

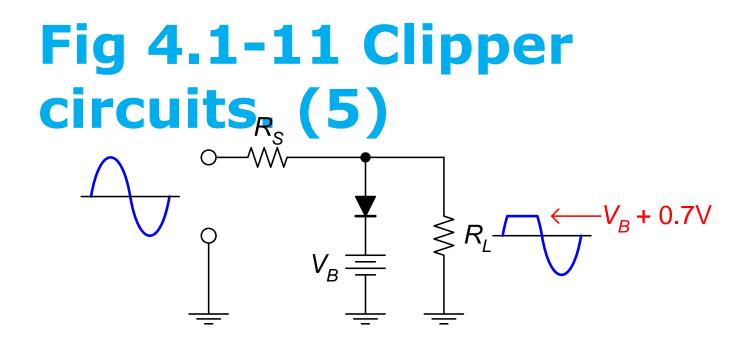

# Fig 4.1-11 Clipper circuits. (2)

Positive series clipper.

Positive shunt clipper.

Biased shunt clipper.

# Fig 4.1-11 Clipper circuits. (6)

#### Adjustable shunt clipper.

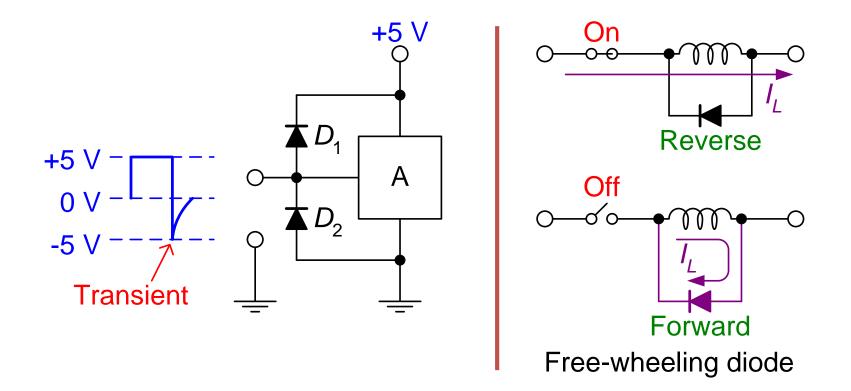

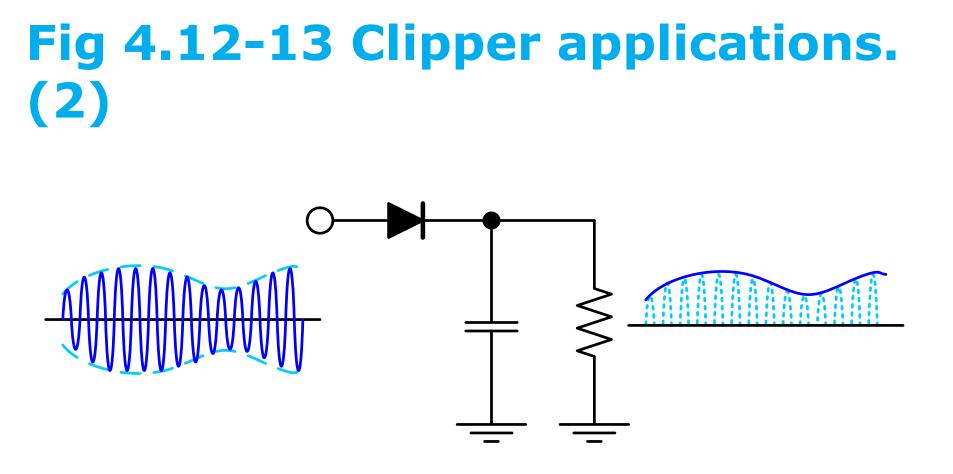

#### Fig 4.12-13 Clipper applications. (1)

**Transient-protection circuits**

#### AM detector

# ANALOG AND DIGITAL ELECTRONICS.

#### UNIT – II BIPOLAR JUNCTION TRANSISTORS

#### Introduction:

<u>Transistor:</u> A Transistor is a three terminal semiconductor device that regulates current or voltage flow and acts as a switch or gate for signals.

#### Why Do We Need Transistors?

Suppose that you have a FM receiver which grabs the signal you want. The received signal will obviously be weak due to the disturbances it would face during its journey. Now if this signal is read as it is, you cannot get a fair output. Hence we need to amplify the signal. Amplification means increasing the signal strength. This is just an instance.

Amplification is needed wherever the signal strength has to be increased. This is done by a transistor. A transistor also acts as a switch to choose between available options. It also regulates the incoming current and voltage of the signals.

#### Transistor characteristics:

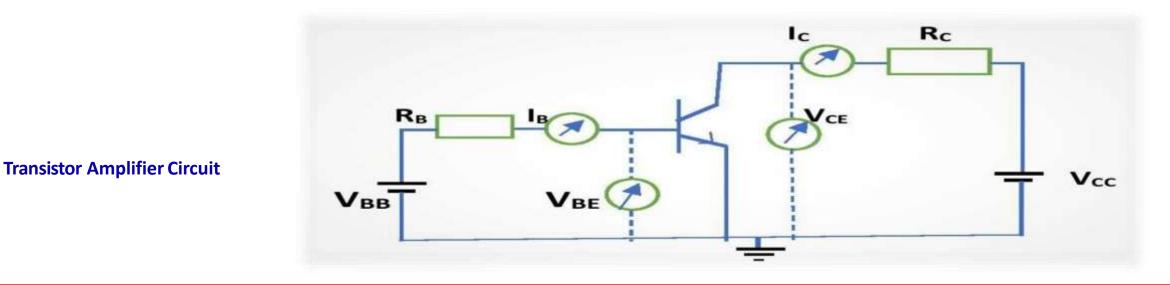

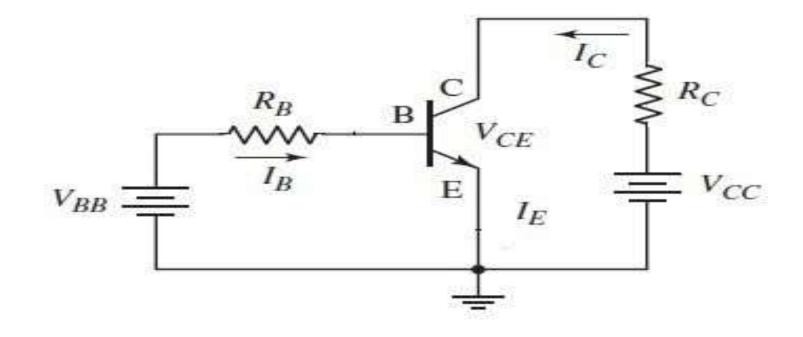

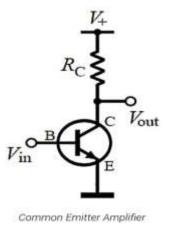

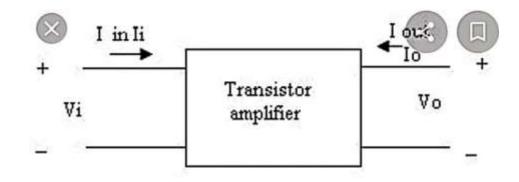

- One can draw the characteristics curves of a Transistor by using the following **Transistor Amplifier circuit**. Here, a NPN transistor is used in common emitter mode.

- $V_{BE}$  is the input voltage,  $V_{CE}$  is the output voltage,  $I_B$  is input current and  $I_C$  is the output current.

- To measure input and output voltages and currents, two voltmeters and two ammeters are used in this circuit.

3

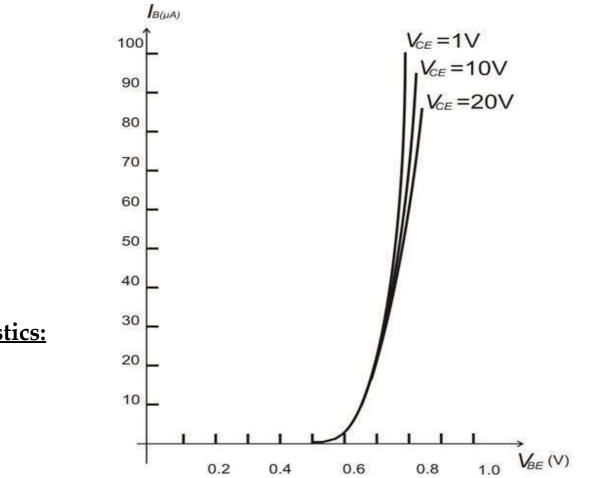

## Input Characteristics of Transistor:

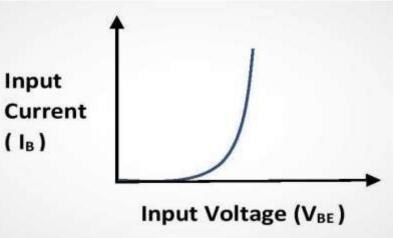

- Input characteristics curve indicates the variation of input current with the input voltage. So, here we will analyze the variation of base current ( $I_B$ ) with the base-to-emitter voltage ( $V_{BE}$ ).

- To draw I<sub>B</sub> vs V<sub>BE</sub> curve we need to ground the output terminal. That means we need to connect collector terminal to emitter terminal as the emitter is already grounded in CE mode. At this condition transistor behaves like a <u>p-n junction diode</u>.

- There is an exponential growth of base current with increase in  $V_{\mbox{\scriptsize BE}}$  .

- So, the I<sub>B</sub> vs V<sub>BE</sub> curve will be similar to diode characteristics curve. Fig.3 gives the Input characteristics curve of a Transistor in CE mode.

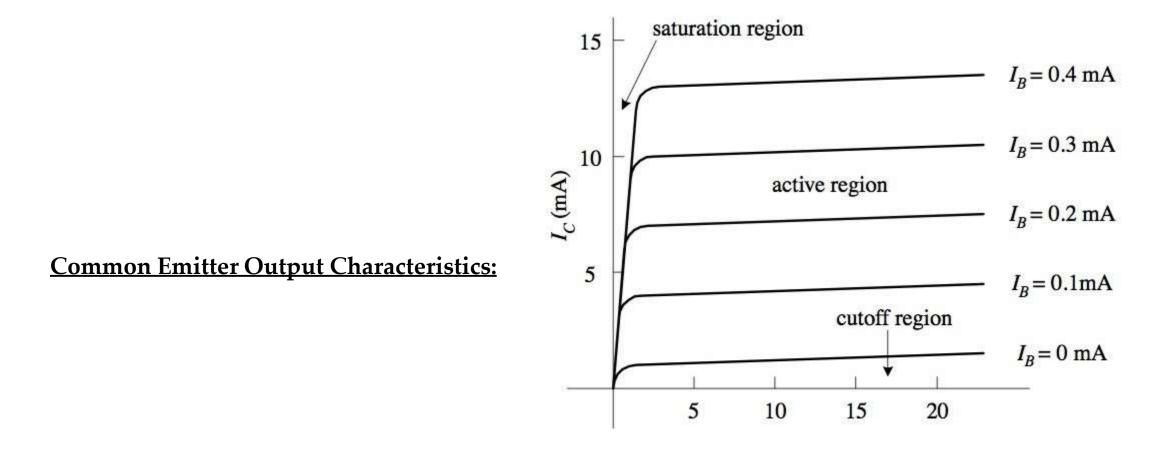

## Output Characteristics of Transistor:

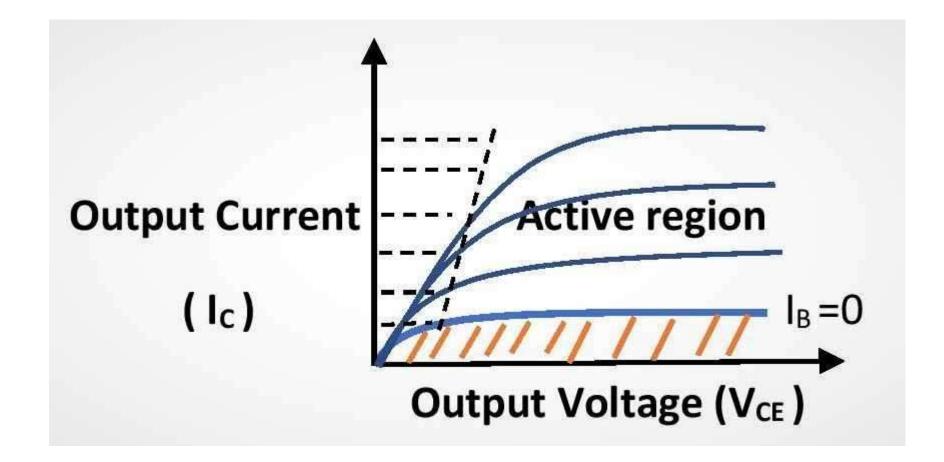

- Output Characteristics curve of a Transistor gives the variation of output current with the change in output voltage.

- In a common emitter transistor collector current is output current and collector-to emitter voltage is the output voltage.

- In the graph one can see that there is a rapid increase of collector current at the beginning and then the collector current becomes almost constant. If we increase  $V_{CE}$  further, the breakdown occurs and then the transistor may be damaged. One can divide the output curve into four regions

- Active Region (the region in which output current becomes almost constant)

- Saturation Region (horizontal dotted lines (—-) in output curve indicates transistor saturation region)

- Cut off region ( / / / / lines in output curve indicates the cut off region)

- Inverted region (appears after breakdown which is not shown in the output curve)

#### **Output Characteristics of Transistor:**

fig(4): Output characteristics curve of Transistor

### Active Region of Transistor

- The region on output curve of a transistor where the output current is almost constant and independent on output voltage is the Active region of Transistor.

- If the base resistance be greater than the maximum allowed value then the transistor operates in Active region.

- One can use **Transistor as an Amplifier** only if it operates in active region.

- Also for the operation in active region, emitter junction should be in forward bias and the collector junction should be in reverse bias.

#### Saturation region of Transistor

- Saturation region is the region on output curve of transistor where the collector current increases rapidly with the slight increase in output voltage.

- To operate the transistor in saturation region, the base resistance should be smaller than the maximum allowed value.

- Also, for the operation in saturation region, both of emitter junction and collector junction should be in forward bias.

- In saturation region, transistor acts like ON stage of a switch.

### Cut Off region of transistor

- In the Cut Off region the base current is almost zero. Therefore, collector current also becomes zero even at higher output voltage.

- To operate a transistor in the cut off region, both of emitter junction and collector junction should be in the reverse bias condition.

- In the cut off region a transistor acts like the OFF stage of a switch.

#### Inverted region of transistor

- This is the inverse of active region. A transistor will operate in inverted region if its emitter junction is in reverse bias and the collector junction is in forward bias.

- In this region, breakdown occurs and collector current increases rapidly. There is no major practical use of transistor in inverted region.

- Therefore, transistor operation in this region is rarely used. This region is not shown in the output diagram.

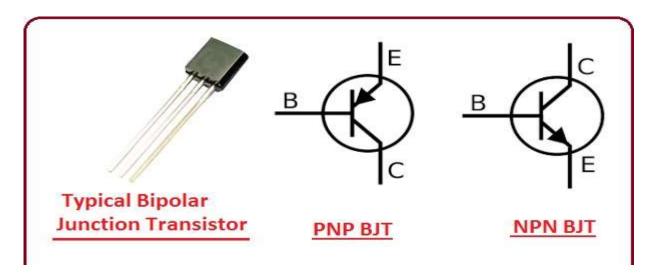

- A bipolar junction transistor is a three terminal device in which operation depends on the interaction of both majority and minority carriers and hence the name bipolar.

- The BJT is analogues to vacuum triode and is comparatively smaller in size. It is used as amplifier and oscillator circuits, and as a switch in digital circuits.

- It has wide applications in computers, satellites and other modern communication systems.

#### Working of Junction Transistor

- In comparison to the emitter and collector, the base of a transistor is made thin and is lightly doped which means that the density of the majority carriers in the base is less than the density of majority carriers in the emitter and collector.

- The flow of current is supplied through the emitter and the collector collects them. For a proper connection between the emitter and the collector, the base provides the interaction for the connectivity.

- In a junction transistor, the arrow points towards the conventional current. In n-p-n transistor's emitter, the arrow points away from the base, and in a p-n-p transistor's emitter, the arrow points towards the base.

- The base-emitter junction is usually forward biased and the base-collector junction is reversed biased when the junction transistor is used in a circuit.

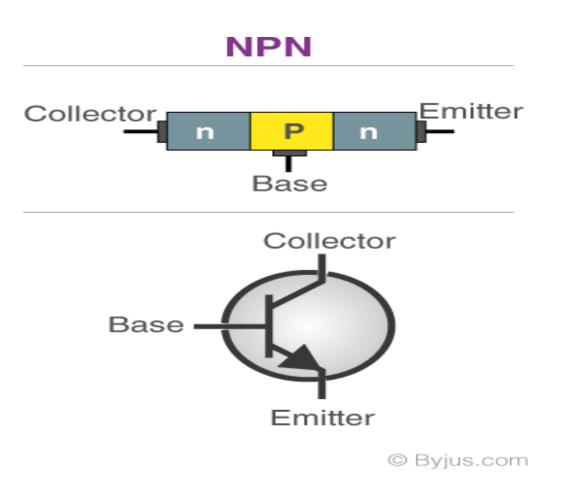

#### NPN transistor

- In an NPN transistor, a p-type semiconductor base is sandwiched between an n-doped emitter and n-doped collector. NPN transistors are the highest used bipolar transistors due to the ease of electron mobility over electron-hole mobility.

- The figure shows the construction and symbol of NPN transistors. The majority charge carriers in an n-p-n transistor are electrons and holes are the minority charge carriers

- . A small amount of current at the base terminal causes a large amount of current to flow from emitter to collector.

- Due to forward biasing of the transistor, the majority charge carriers in the emitter are repelled towards the base.

- The electron-hole recombination at the base is very small in the base region and most of the electrons cross into the collector region.

#### NPN transistor

#### **PNP** transistor

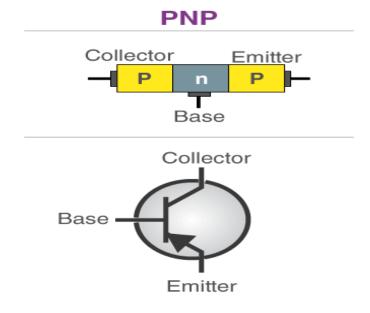

- In a PNP transistor, an n-type semiconductor base is sandwiched between a p-doped emitter and p-doped collector.

- In this type of transistors, holes are the majority carriers and electrons are the minority carriers.

- In a PNP transistor, the emitter is forward biased and the collector is reverse biased.

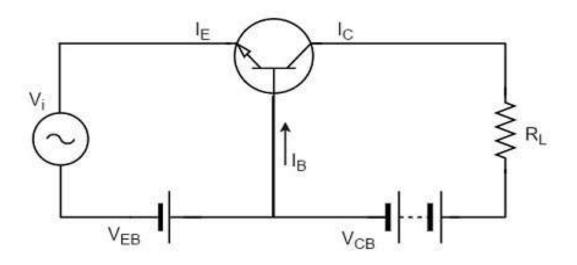

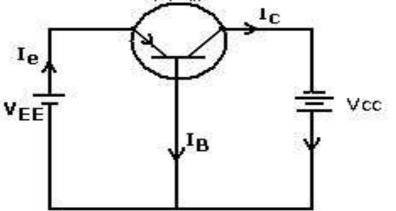

#### Transistor as an Amplifier:

• For a transistor to act as an amplifier, it should be properly biased. Here, let us focus how a transistor works as an amplifier.

#### **Transistor Amplifier**

- A transistor acts as an amplifier by raising the strength of a weak signal.

- The DC bias voltage applied to the emitter base junction, makes it remain in forward biased condition.

- This forward bias is maintained regardless of the polarity of the signal.

- The below figure shows how a transistor looks like when connected as an amplifier.

#### Transistor as an Amplifier:

- The low resistance in input circuit, lets any small change in input signal to result in an appreciable change in the output.

- The emitter current caused by the input signal contributes the collector current, which when flows through the load resistor R<sub>L</sub>, results in a large voltage drop across it.

- Thus a small input voltage results in a large output voltage, which shows that the transistor working as an amplifier.

## Transistor configurations:

- We know that generally the transistor has three terminals emitter (E), base (B) and collector.

- But in the circuit connections we need four terminals, two terminals for input and another two terminals for output.

- To overcome these problems we use one terminal as common for both input and output actions

- Using this property we construct the circuits and these structures are called transistor configurations.

- Generally there are three different configurations of transistors and they are common base (CB) configuration, common collector (CC) configuration and common emitter (CE) configuration.

## Transistor configurations:

- The behavior of these three different configurations of transistors with respect to gain is given below.

- Common Base (CB) Configuration: no current gain but voltage gain

- Common Collector (CC) Configuration: current gain but no voltage gain

- Common Emitter (CE) Configuration: current gain and voltage gain

## **Common Base Configuration:**

- The voltage is applied at the junction of the emitter and the base. Here the emitter and the base are referred to as the input side and the collector is known for the output side of the circuit connection.

- The characteristic of the input is based on the voltage applied at the terminals base and the emitter and the current at the emitter terminal.

- The output characteristic for this configuration is based on the parameters of the voltage applied at the terminals of the base and the collector and the current generated at the collector terminal.

<u>Common Base Configuration</u>:

## Input characteristics of CB:

- The input characteristics for this type of configuration is measured by the variation at the voltage value at the terminals of the emitter and the base at different points by keeping the voltage value at the collector and the base as constant.

- From this the input value of the current that is at emitter is measured. Based on which the graph is plotted.

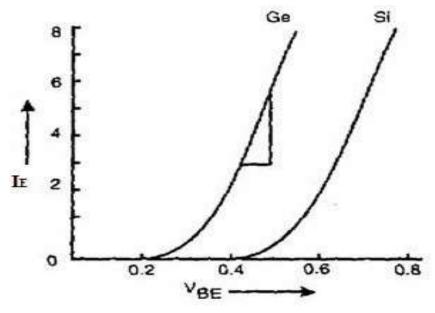

**Common Base Input Characteristics**

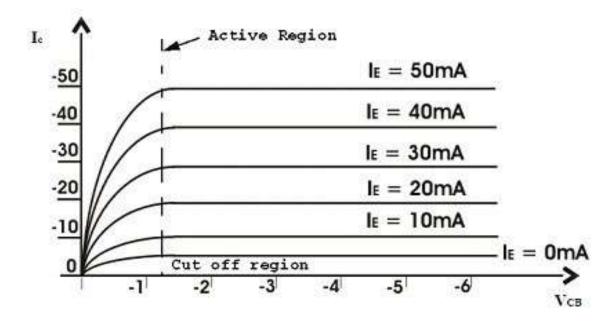

## Output characteristics of CB:

• The graph is plotted between the voltage at the output and the current by keeping the input value of the current at the constant gives the output characteristics for this configuration.

**Common Base Output Characteristics:**

# Common Collector Configuration:

- This is the configuration in which the collector terminal is made common for both the input and the output connections of the circuit.

- In this the voltage at the terminal emitter follows the voltage of the base terminal. Hence this circuit is referred to as the emitter following circuit. The input value of the impedance is high.

- The considered input signals are applied in between the terminals of the collector and the base. The output is to be taken or considered in between the terminals of the collector and the emitter.

**Common Collector Configuration:**

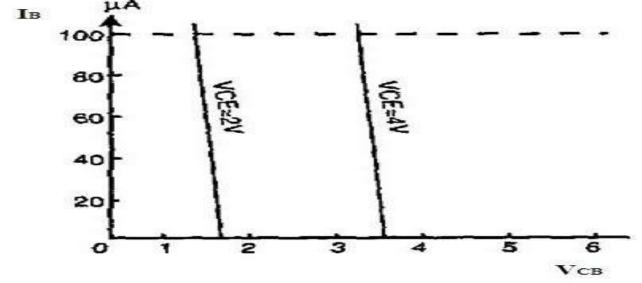

## Input characteristics of CC:

- The characteristics for this type of configuration are very different in comparison with other configurations.

- Here the voltage at the collector and the base terminal is determined by the level of the voltage at the emitter and the collector.

- By maintaining voltage at the collector and the emitter at the constant values the graph is plotted between the parameters of the base current and the voltage value at the collector and the base terminals.

**Common Collector Input Characteristics:**

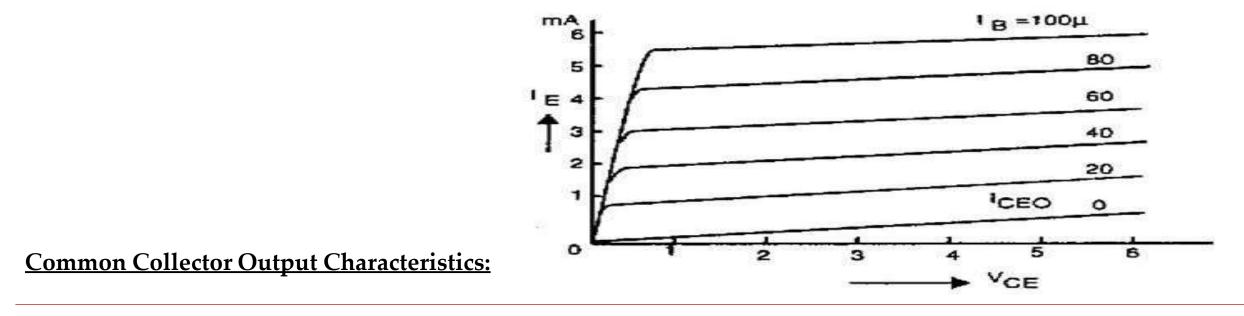

# Output characteristics of CC:

- As the collector configuration is known to follow the emitter configuration the operation of the output is similar to that of the emitter configuration.

- In this configuration if there is no voltage is applied at the base terminal there will be no amount of current flow is evident in the circuitry.

- The graph is plotted between the emitter current and the voltage at the terminals of the collector and the emitter by maintaining the value at the base current at constant.

- This is the most widely used configuration because of the gain in both voltage and the currents increments the gain value of the power.

- In this the voltage of the input is applied in between the terminals of the emitter and the base. The output is taken across the terminals of emitter and the collector. Hence this circuit is inverting type.

- The gain between the ratio of current at the collector terminal and the emitter terminal is measured in terms of alpha. The gain for the ratio between the currents of the collector terminal and the base is measured in terms of beta.

- The generated output signal has the shifting in phase about 180 degrees that represents the input and the output signals are inversely related in terms of phases.

#### **Common Emitter Configuration**:

## Input characteristics of CE:

• The graph is plotted between the current at the base and the voltage value at the terminals of base and the emitter.

**Common Emitter Input Characteristics:**

## Output characteristics of CE:

• The graph is plotted between the values of the collector current and the voltage value of the terminals of collector and the emitter.

# Comparison of CB,CE,CC transistor configurations:

| S.No. | Characteristic                   | Common base                                   | Common emitter                    | Common collector             |

|-------|----------------------------------|-----------------------------------------------|-----------------------------------|------------------------------|

| 1.    | Input resistance                 | Very low (20 Ω)                               | Low (1 k $\Omega$ )               | High (500 kΩ)                |

| 2.    | Output resistance                | Very high (1 $M\Omega$ )                      | High (40 k $\Omega$ )             | Low (50 Ω)                   |

| 3.    | Input current                    | l <sub>E</sub>                                | l <sub>B</sub>                    | l <sub>B</sub>               |

| 4.    | Output current                   | I <sub>C</sub>                                | lc                                | l <sub>E</sub>               |

| 5.    | Input voltage applied<br>between | Emitter and base                              | Base and emitter                  | Base and collector           |

| 6.    | Output voltage taken<br>from     | Collector and base                            | Collector and emitter             | Emitter and collector        |

| 7.    | Current amplification factor     | $\alpha_{dc} = I_C / I_E$                     | $\beta_{dc} = I_C / I_B$          | $\gamma_{dc} = I_E / I_B$    |

| 8.    | Current gain                     | Less than unity                               | High (20 to few hundreds)         | High (20 to few<br>hundreds) |

| 9.    | Voltage gain                     | Medium                                        | Medium                            | Low                          |

| 10.   | Amplifications                   | At the input stage of<br>multistage amplifier | For audio signal<br>amplification | For impedance<br>matching    |

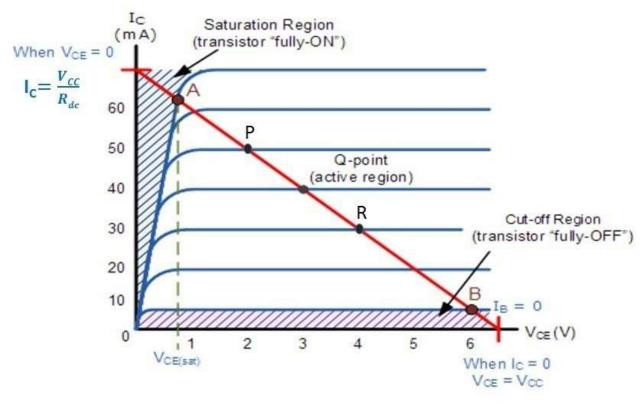

# Operating point in transistor:

<u>Definition:</u> The point which is obtained from the values of the IC (collector current) or VCE (collector-emitter voltage) when no signal is given to the input is known as the 'operating point' or 'Q-point' in a transistor.

- It is called operating point because variations of IC (collector current) and VCE (collectoremitter voltage) takes place around this point when no signal is applied to the input.

- The operating point is also called quiescent (silent) point or simply Q-point because it is a

point on IC VCE characteristic when the transistor is silent or no input signal is applied to

the circuit.

- The operating point can be easily obtained by the DC load line method. The DC load line is shown in below graph.

## Operating point in transistor:

# DC LOAD LINE AND OPERATING POINT

#### What is Transistor Biasing?

- Transistor Biasing is the process of setting a transistor's DC operating voltage or current conditions to the correct level so that any AC input signal can be amplified correctly by the transistor.

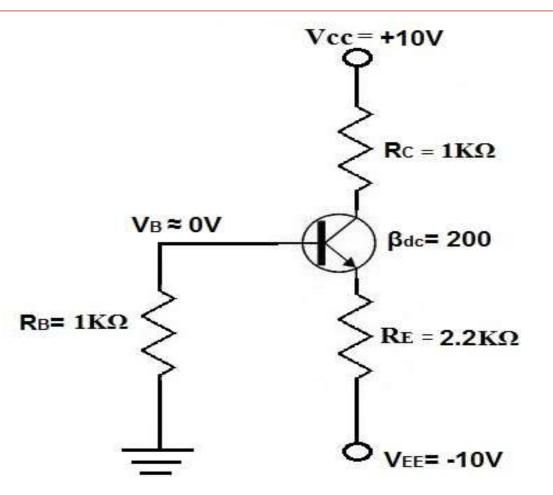

- One way to bias a BJT transistor is a method called emitter bias.

- Emitter bias is a very good and stable way to bias transistors if both positive and negative power supplies are available. Emitter bias fluctuates very little with temperature variation and transistor replacement.

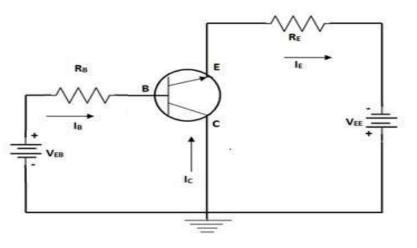

## Self bias of a Transistor:

Beside is a BJT transistor receiving emitter bias:

- You can see how that both positive and negative voltage supplies are necessary to bias a transistor in this way.

- Positive voltage is fed to the collector of the transistor and negative voltage is fed to the emitter.

## Calculations:

- Assuming the above is a silicon transistor, the voltage drop across the base emitter is equal to 0.7v

- To calculate the emitter current(IE):

$$IEQ = \frac{\frac{VEE - VBE}{RB}}{(\beta_{dc})} + RE$$

- So in the circuit above, the emitter current calculation is:  $IE=(10V - 0.7V)/(2.2K\Omega + (1K\Omega/200))=4.22mA$

- To calculate the collector voltage, VC, the formula is

#### $VC = VCC - ICRC = 10V - (4.23mA \times 1K\Omega) = 5.77V$

- Again, emitter bias is an effective way to bias a BJT transistor.

- However, the voltage divider bias is still the most popular way to do so, while base bias is the least popular way because of the instability it provides if β changes.

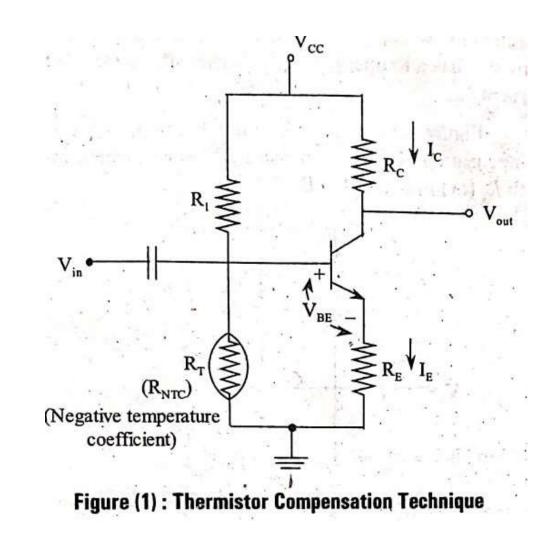

## **Bias Compensation:**

Bias compensation is of two techniques and they are;

- 1. Using thermistors

- 2. Using sensitors

#### Bias compensation using Thermistors:

- In this method, a temperature sensitive resistive element called "thermistor" is used.

- There are elements of negative temperature coefficient whose resistance decreases with increase in temperature.

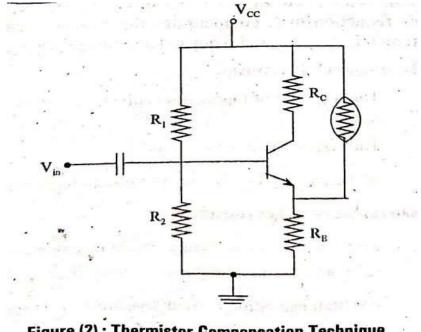

- There are two for bias compensation using thermistor and they are;

- i. One method is carried out by replacing the "R2" resistor with thermistor "Rt" in a selfbias circuit as shown in figure.

ii. In the second method, the thermistor is connected between the supply voltage Vcc and emitter as shown in figure.

Figure (2) : Thermistor Compensation Technique

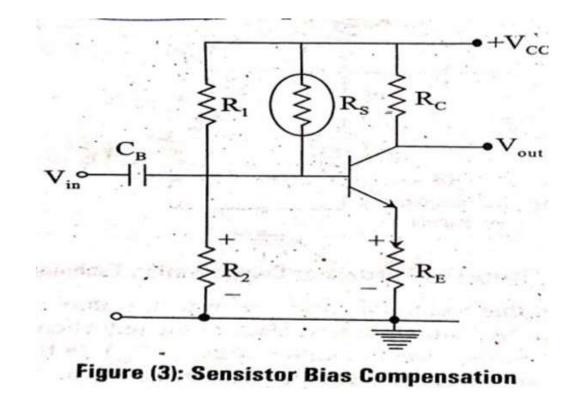

#### Bias compensation using sensistor:

- Sensistor is a temperature sensitive resistor with a positive temperature coefficient, which is used in transistor compensation.

- The sensistor has a temperature coefficient of resistance that is +0.7 percent/c.

- The below figure shows the circuit when sensistor is used as a compensating element.

#### Thermal runway and stability:

<u>Thermal runaway</u>: The expression for the collector current of common emitter circuit is given as (equation 1).

- When the temperature raises, the parameters "B", Icba and Ib in equation 1 also increase.

- The reverse saturation current Icbo increases with rise in temperature, Icbo gets doubles.

- Initially the collector base junction temperature is increased by collector current "Ic" which in turn increases Icbo.

- •This process becomes cumulative and leads to "Thermal runaway".

#### Condition for Thermal stability:

- To avoid thermal runaway the required condition is that the rate at which heat is releaded at collector junction must not exceed the rate at which the heat can be dissipated under steady state condition (equation 2).

- Since the steady state temperature rise at collector junction is propotional to the power dissipated at the junction (equation 3).

a

I.e.,

$$\Delta T = T_{T} - T_{A} = \Theta P_{D}$$

where,

$T_{T} = Junction temp (°c)$

$T_{A} = Ambiert temp (°c)$

$P_{D} = Dissipate power (watts)$

$\Theta = Thermal resistance$

$T_{T} - T_{A} = \Theta P_{D} - (2)$

Differentiating  $eq(3) \cdot (\omega \cdot v \cdot t - T_{T})$

$\Rightarrow 1 = \Theta \frac{dP_{D}}{dT_{T}}$

$\frac{dP_{D}}{dT_{T}} = \frac{1}{\Theta} - (2)$

Then, from  $equ(2)$

$\frac{dP_{D}}{dT_{T}} < \frac{1}{\Theta}$  is condition which must be

• Thus the transistor cannot runaway below a specified ambient temperature under any biasing condition.

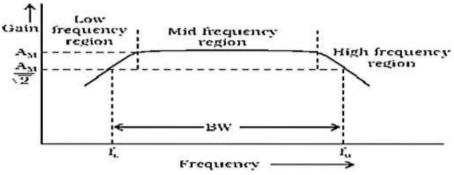

#### **Common emitter amplifier frequency response:**

• Basic bi-polar junction transistor (BJR) amplifier topologies, typically used as a voltage amplifier.

#### **CE** amplifier frequency response:

- The voltage gain of CE amplifier varies with signal frequency.

- The curve drawn between voltage gain and the signal frequency of an amplifier is known as frequency response.

Frequency Response

- i. At low frequencies (<Fl): The reactance of coupling capacitor C2 is relatively high and hence very small part of signal will pass from the amplifier stage to the load.

- ii. Due to this, it causes drop off of voltage gain at low frequencies.

- iii. The reactance of coupling capacitor C2 is very small and it behaves as short circuit. This increases the loading effect of the amplifier stage.

iv. Due to this, the voltage gain drops off at high frequency.

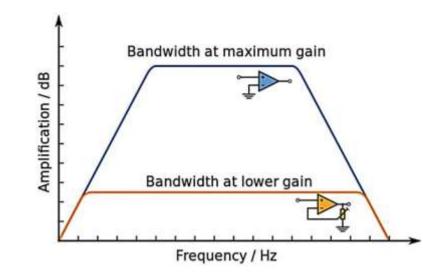

#### Gain bandwidth product:

• The gain bandwidth product, GBW is defined as the product of the open loop voltage gain and the frequency at which it is measured. GBW is expressed in units of Hertz.

- Relevance to this quantity is commonly specified for operational amplifiers, and allows circuit designers to determine the maximum gain that can be extracted from the device for a given frequency and vice versa.

- Gain and bandwidth in an amplifier are inversely proportional to each other and their relationship is summarized as the unity gain bandwidth. Unity gain bandwidth defines the frequency at which the gain of an amplifier is equal to 1.

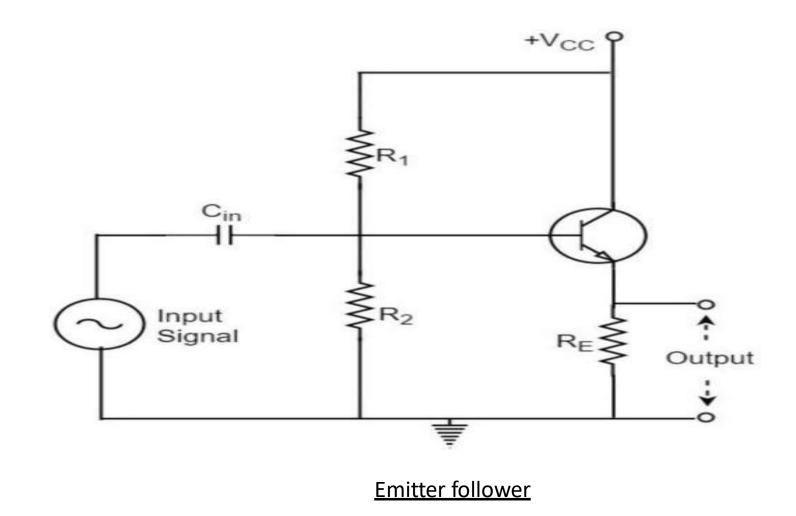

#### **Emitter follower:**

Emitter follower circuit has a prominent place in feedback amplifiers. Emitter follower is a case of negative current feedback circuit. This is mostly used as a last stage amplifier in signal generator circuits.

The important features of Emitter follower are:

- It has high input impedance.

- It has low output impedance.

- It is ideal circuit for impedance matching.

#### Voltage gain of emitter follower:

• As the emitter follower circuit is a prominent one, let us try to get the get equation for the voltage gain of an emitter follower circuit. Our emitter follower circuit looks as follows-

Voltage gain of emitter follower

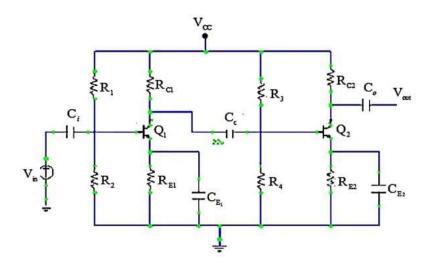

#### **RC** coupled amplifier:

- RC coupling is the most widely used method of coupling in multistage amplifiers. In this case the resistance R is the resistor connected at the collector terminal and the capacitor C is connected in between the amplifiers. It is also called a blocking capacitor, since it will block DC voltage.

- The frequency response of RC amplifier provides constant gain over a wide frequency range, hence most suitable for audio applications.

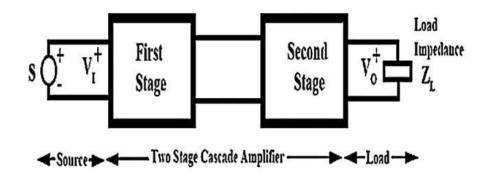

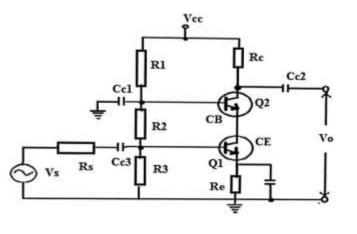

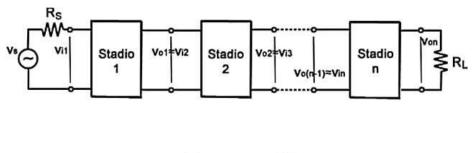

#### Two cascaded CE amplifier:

• The two stages of cascaded CE(common emitter) are shown in the following circuit. Here the voltage divider can be formed by using the input and output resistances of the first and next stage.

cascade-amplifier-circuit

- A multistage amplifier design using CE (common emitter) as the primary stage as well as CB (common base) as the second stage is named as a cascade amplifier. The connection between cascade & cascade can also possible using FET amplifiers.

- A multistage amplifier using two or more single stage common emitter amplifier is called as cascade amplifier.

multistage-amplifier

• The design of the multistage CE amplifier was done using the designed single stage CE amplifier as the basic configuration.

A multistage CE amplifier configuration design

#### **Transistor at low frequencies:**

- The transistor can be employed as an amplifying device, that is, the output ac power is greater than the input ac power. The factor that permits an ac power output greater than the input ac power is the applied DC power.

- Thus to simplify the analysis of BJT, its operation is restricted to the linear V-I characteristics around the Q-point that is in the active region.

- The factor that permits an ac power output greater than the input AC power is the applied DC power. The amplifier is initially biased for the required DC voltages and currents.

# ANALOG AND DIGITAL ELECTRONICS.

#### UNIT – III FET's and Digital Circuits

#### Introduction:

- The Field effect transistor is abbreviated as FET, it is an another semiconductor device like a BJT which can be used as an amplifier or switch.

- FET is also a three terminal device, labelled as source, drain and gate.

- The material that connects the source to drain is referred to as the channel.

- FET operation depends only on the flow of majority carriers ,therefore they are called uni polar devices.

- As FET has conduction through only majority carriers it is less noisy than BJT.

- FETs are much easier to fabricate and are particularly suitable for ICs because they occupy less space.

- FET amplifiers have low gain bandwidth product due to the junction capacitive effects and produce more signal distortion except for small signal operation.

- The performance of FET is relatively unaffected by ambient temperature changes. As it has a negative temperature coefficient at high current levels, it prevents the FET from thermal breakdown.

## Classification of FET:

There are two major categories of field effect transistors:

1. Junction Field Effect Transistors

2.MOSFETs

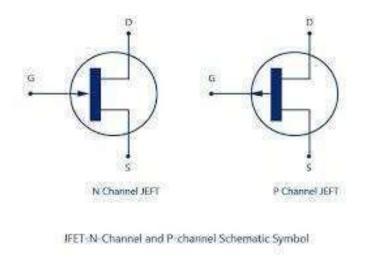

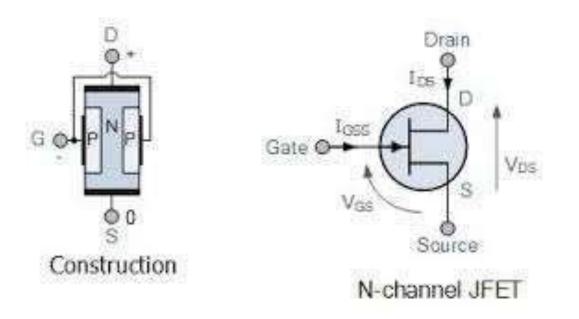

#### **1. Junction Field Effect Transistors:**

When the channel is of N-type the JFET is referred to as an N-channel JFET, when the channel is of P-type the JFET is referred to as P-channel JFET.

•The schematic symbols for the N-channel and P-channel JFETs are shown in the figure.

• A piece of N- type material, referred to as channel has two smaller pieces of P-type material attached to its sides, forming PN junctions. The channel ends are designated as the drain and source. And the two pieces of P-type material are connected together and their terminal is called the gate. Since this channel is in the N-type bar, the FET is known as N-channel JFET.

The overall operation of the JFET is based on varying the width of the channel to control the drain current.

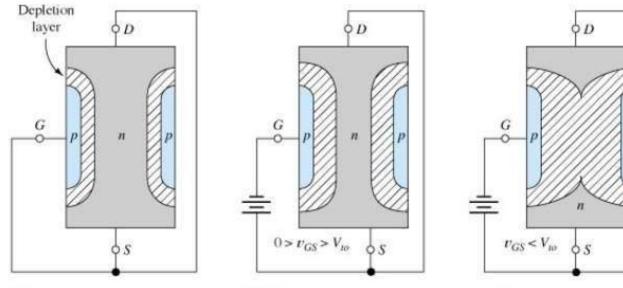

### **N-Channel JFET Operation**

(a) Bias is zero and depletion layer is thin; low-resistance channel exists between the drain and the source (b) Moderate gate-to-channel reverse bias results in narrower channel (c) Bias greater than pinch-off voltage; no conductive path from drain to source

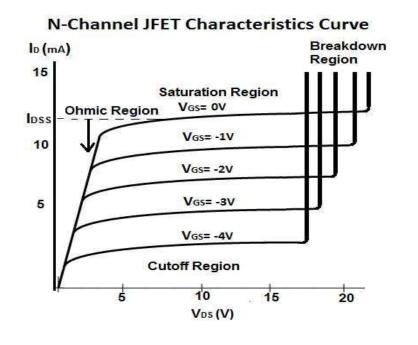

# Characteristics Of N-Channel JFET:

NRCM

The family of curves that shows the relation between current and voltage are known as characteristic curves.

- There are two important characteristics of a JFET.

- 1) Drain or VI Characteristics

- 2) Transfer characteristics

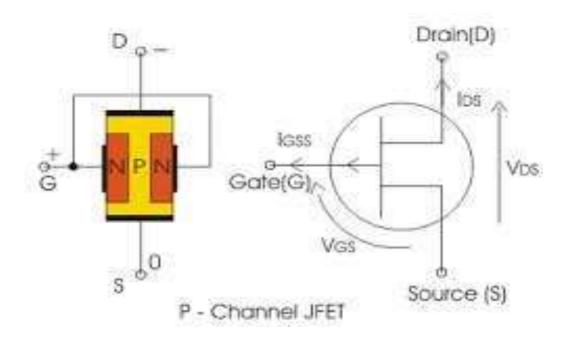

## Construction Of P-Channel JFET:

• The construction diagram of P channel junction field effect transistor (JFET) is shown in above figure. Its construction is similar to the N channel JFET excepts that it consist of a P type silicon bar with two N type heavily doped regions diffused on opposites sides of its middle part. The JFET in which the current conduction takes place only due to holes as majority charge carriers is known as <u>P channel JFET</u>.

# Operation Of P-Channel JFET:

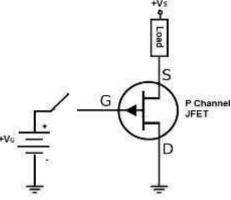

- When no voltage is applied to the gate of a P-Channel JFET, current (holes) flows freely through the central P-channel. This is why JFETs are referred to as "normally on" devices. Even without any voltage, they conduct current across from source to drain.

- To turn on a P-channel JFET, apply a positive voltage VS to the source terminal of the transistor with no voltage applied to the gate terminal of the transistor. This will allow a current to flow through the drain-source channel. If the gate voltage, VG, is 0V, the drain current is at its largest value for safe operation, and the JFET is in the ON active region.

- To turn off a P-channel JFET, there are 2 steps you can take. You can either cut off the bias positive voltage, VS, that powers the source terminal. Or you can apply a positive voltage to the gate. When a positive voltage is applied to the gate, the source-drain current is reduced. As the gate voltage, VG, becomes more positive, the current lessens and lessens until it completes reaches cutoff, which is when then JFET is in the Off condition and no current conducts across from source to drain. This stops all drain-source current flow.

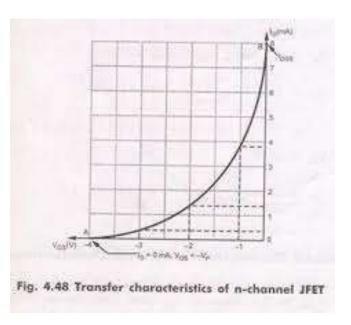

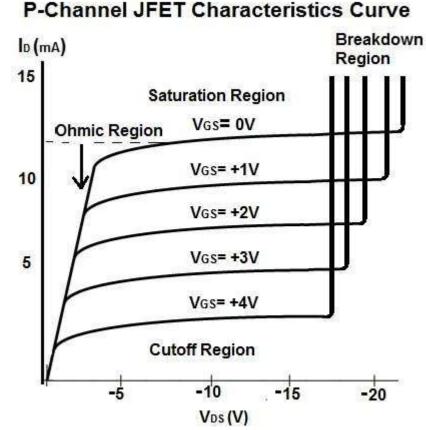

## **Characteristics Of P-Channel JFET:**

- The characteristics curve of a P Channel JFET transistor shown below is the the graph of the drain current, ID versus the ٠ gate-source voltage, VGS.

#### P-Channel JFET Characteristics Curve

The Regions that make this characteristic curve are the following:

**Cutoff Region**- This is the region where the JFET transistor is off, meaning no drain current, ID flows through the source-drain region.

**Ohmic Region**- This is the region where the JFET transistor begins to show some resistance to the drain current ID that is beginning to flow through the source-drain region. This is the only region in the curve where the response is linear.

**Saturation Region**- This is the region where the JFET transistor is fully operational and maximum current is flowing. During this region, the JFET is On and active.

**Breakdown Region**- This is the region where the voltage that is supplied to the source terminal of the transistor exceeds the necessary maximum. At this point, the JFET loses its ability to resist current because too much voltage is applied across its source-drain terminals. The transistor breaks down and current flows from source to drain.

- The gate to source junction of a JFET is never allowed to become forward biased because the gate material is not designed to handle any significant amount of current. If the junction is allowed to become forward biased, current is generated through the gate material. This current may destroy the component.

- There is one more important characteristic of JFET reverse biasing i.e. J FET 's have extremely high characteristic gate input impedance. This impedance is typically in the high mega ohm range. With the advantage of extremely high input impedance it draws no current from the source. The high input impedance of the JFET has led to its extensive use in integrated circuits. The low current requirements of the component makes it perfect for use in ICs. Where thousands of transistors must be etched on to a single piece of silicon. The low current draw helps the IC to remain relatively cool, thus allowing more components to be placed in a smaller physical area.

### JFET Parameters:

- The electrical behavior of JFET may be described in terms of certain parameters. Such parameters are obtained from the characteristic curves.

- **1.AC Drain resistance(rd):** It is also called dynamic drain resistance and is the a.c. resistance between the drain and source terminal, when the JFET is operating in the pinch off or saturation region. It is given by the ratio of small change in drain to source voltage  $\Delta V$ ds to the corresponding change in drain current  $\Delta Id$  for a constant gate to source voltage Vgs.

Mathematically it is expressed as  $rd=\Delta Vds/\Delta Id$  where Vgs is held constant.

2. TRANCE CONDUCTANCE (gm): It is also called forward transconductance. It is given by the ratio of small change in drain current ( $\Delta$ Id) to the corresponding change in gate to source voltage ( $\Delta$ Vds).

Mathematically the transconductance can be written as  $gm=\Delta Id/\Delta Vds$ .

**3. AMPLIFICATION FACTOR** ( $\mu$ ): It is given by the ratio of small change in drain to source voltage ( $\Delta V$ ds) to the corresponding change in gate to source voltage ( $\Delta V$ gs )for a constant drain current (Id).

Thus  $\mu = \Delta V ds / \Delta V gs$  when Id held constant.

The amplification factor  $\mu$  may be expressed as a product of transconductance (gm) and ac drain resistance (rd)

$\mu = \Delta V ds / \Delta V gs = gm rd$

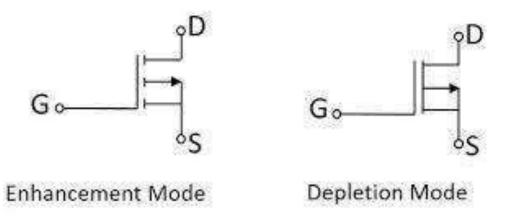

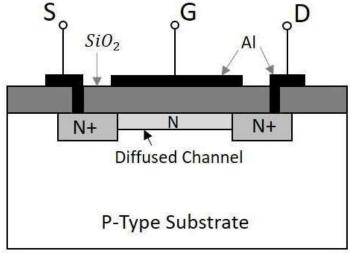

### MOSFET:

These are further sub divided in to P- channel and N-channel devices.

MOSFETs are further classified in to two types

- 1. Enhancement MOSFETs and

- 2. Depletion MOSFETs

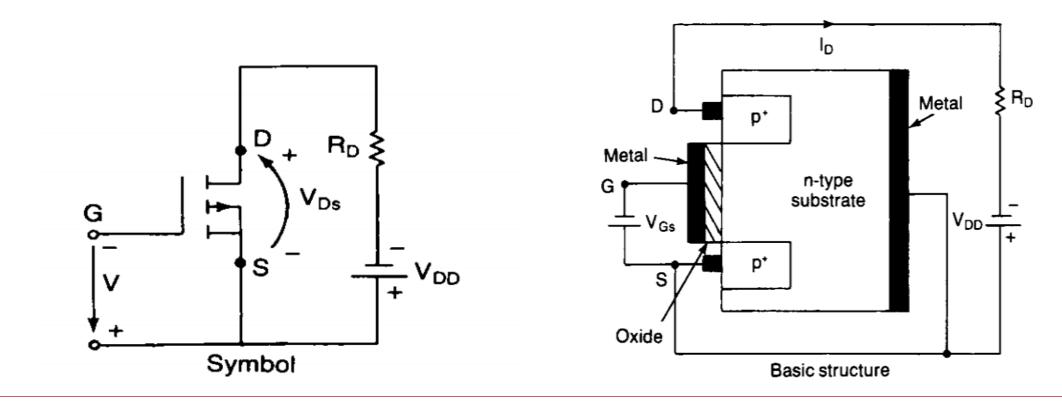

Symbols of P-Channel MOSFET

•D-MOSFETS can be operated in both the depletion mode and the enhancement mode. E MOSFETS are restricted to operate in enhancement mode. The primary difference between them is their physical construction.

A thin layer of insulation silicon dioxide (SIO2) is grown over the surface of the structure, and holes are cut into oxide layer, allowing contact with the source and drain. Then the gate metal area is overlaid on the oxide, covering the entire channel region. Metal contacts are made to drain and source and the contact to the metal over the channel area is the gate terminal.

The metal area of the gate, in conjunction with the insulating dielectric oxide layer and the semiconductor channel, forms a parallel plate capacitor. The insulating layer of sio2 Is the reason why this device is called the insulated gate field effect transistor.

Structure of N-channel MOSFET

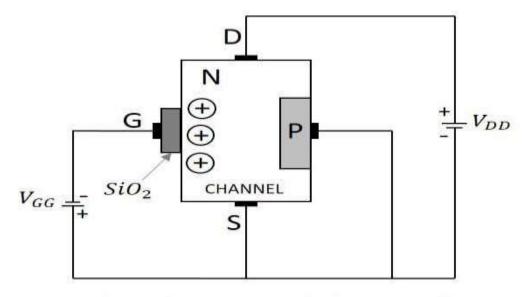

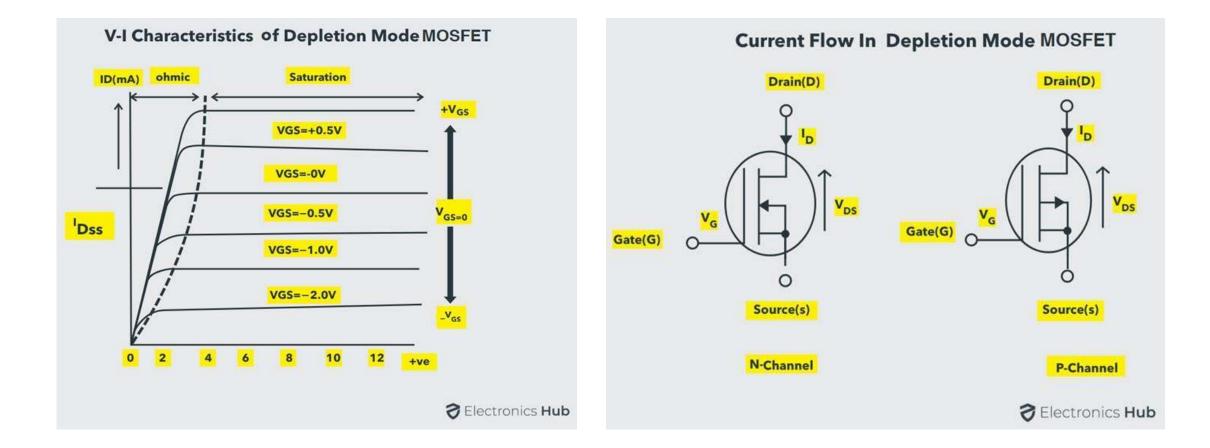

When no voltage is applied between gate and source, some current flows due to the voltage between drain and source. Let some negative voltage is applied at  $V_{GG}$ . Then the minority carriers i.e. holes, get attracted and settle near SiO<sub>2</sub> layer. But the majority carriers, i.e., electrons get repelled.

The channel nearer to drain gets more depleted than at source like in FET and the current flow decreases due to this effect. Hence it is called as depletion mode MOSFET.

Working of MOSFET in depletion mode

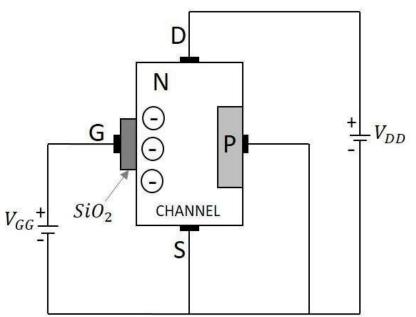

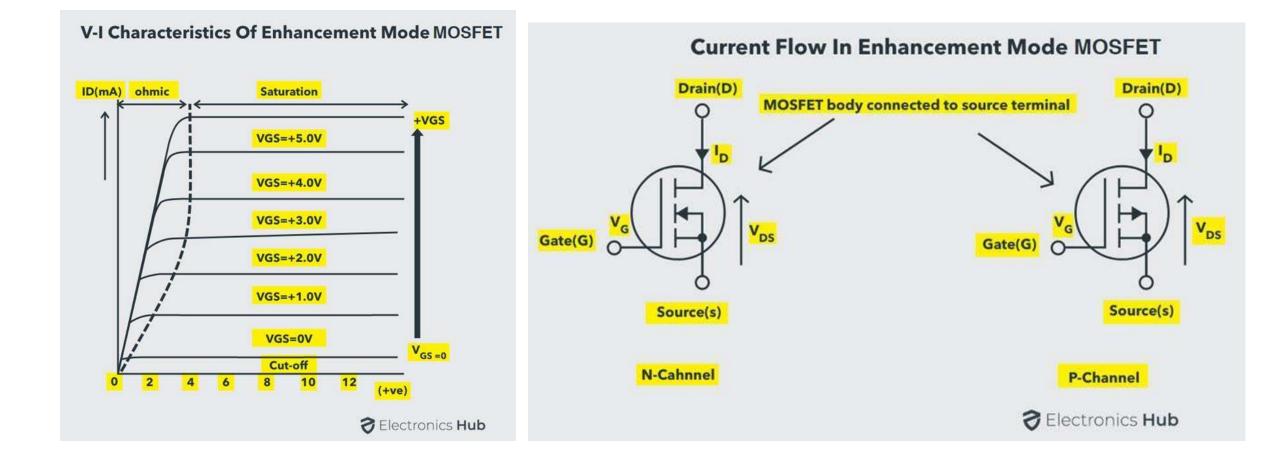

When this positive potential is further increased, the current  $I_D$  increases due to the flow of electrons from source and these are pushed further due to the voltage applied at  $V_{GG}$ . Hence the more positive the applied  $V_{GG}$ , the more the value of drain current  $I_D$  will be. The current flow gets enhanced due to the increase in electron flow better than in depletion mode. Hence this mode is termed as **Enhanced Mode MOSFET**.

Working of MOSFET in Enhancement mode

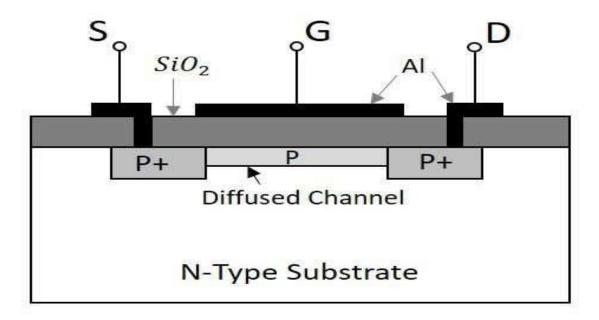

The construction and working of a PMOS is same as NMOS. A lightly doped **n-substrate** is taken into which two heavily doped **P**+ **regions** are diffused. These two P+ regions act as source and drain. A thin layer of  $SiO_2$  is grown over the surface. Holes are cut through this layer to make contacts with P+ regions, as shown in the following figure.

Structure of P-channel MOSFET

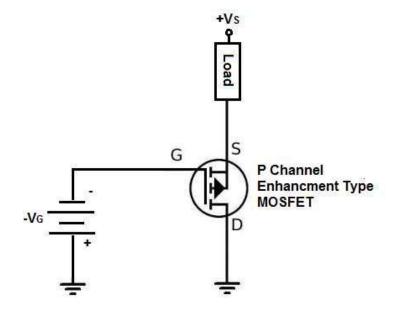

# Working of P-Channel MOSFET-Depletion Mode

In p channel depletion MOSFET channel is already created between drain and source. As we know for MOSFET gate terminal has a thin <u>metal oxide layer</u>. Generally, Sio2 used as this metal oxide layer. Now we apply the negative voltage at the gate terminal. Due to the capacitive effects electrons are repealed each other and shifted to the p channel. In this way here depletion occurs so it named depletion MOSFET. As per figure you can see we applied negative gate voltage and positive drain voltage. This is the basic working of p channel depletion MOSFET.

# Working of P-Channel MOSFET-Enhancement Mode

- To turn on a P-Channel Enhancement-type MOSFET, apply a positive voltage VS to the source of the MOSFET and apply a negative voltage to the gate terminal of the MOSFET (the gate must be sufficiently more negative than the threshold voltage across the drain-source region (VG<vDS). This will allow a current to flow through the source-drain channel.

- To turn off a P-channel enhancement type MOSFET, there are 2 steps you can take. You can either cut off the bias positive voltage, VS, that powers the source. Or you can turn off the negative voltage going to the gate of the transistor.

### Depletion Mode MOSFET

## Enhancement Mode MOSFET

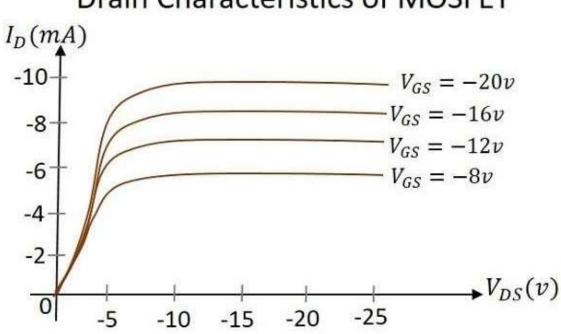

# Drain Characteristics Of MOSFET

The drain characteristics of a MOSFET are drawn between the drain current  $I_D$  and the drain source voltage  $V_{DS}$ . The characteristic curve is as shown below for different values of inputs.

Actually when  $V_{DS}$  is increased, the drain current  $I_D$  should increase, but due to the applied  $V_{GS}$ , the drain current is controlled at certain level. Hence the gate current controls the output drain current.

Drain Characteristics of MOSFET

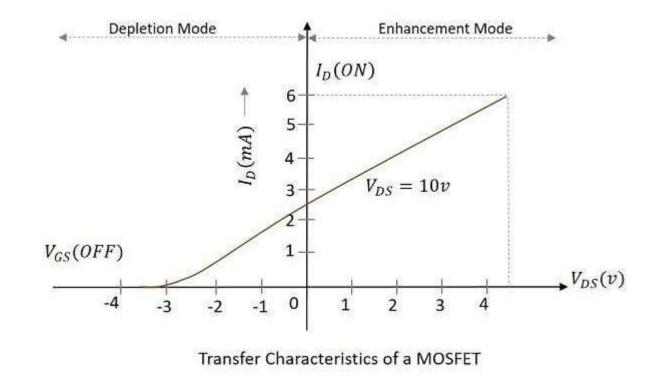

## Transfer Characteristics Of MOSFET

Transfer characteristics define the change in the value of  $V_{DS}$  with the change in  $I_D$  and  $V_{GS}$  in both depletion and enhancement modes. The below transfer characteristic curve is drawn for drain current versus gate to source voltage.

# Application Of MOSFET

- One of the primary contributions to electronics made by MOSFETs can be found in the area of digital (computer electronics). The signals in digital circuits are made up of rapidly switching dc levels. This signal is called as a rectangular wave ,made up of two dc levels (or logic levels). These logic levels are 0V and +5V.

- A group of circuits with similar circuitry and operating characteristics is referred to as a logic family. All the circuits in a given logic family respond to the same logic levels, have similar speed and power handling capabilities, and can be directly connected together. One such logic family is complementary MOS (or CMOS) logic. This logic family is made up entirely of MOSFETs.

- MOSFET amplifiers are extensively used in radio frequency applications.

- DC motors can be regulated by power MOSFETs.

- It acts as a passive element like resistor, capacitor and inductor.

- High switching speed of MOSFETs make it an ideal choice in designing chopper circuits.

# Comparison Of Mosfet With JFET

- In enhancement and depletion types of MOSFET, the transverse electric field induced across an insulating layer deposited on the semiconductor material controls the conductivity of the channel.

- In the JFET the transverse electric field across the reverse biased PN junction controls the conductivity of the channel.

- The gate leakage current in a MOSFET is of the order of 10-12A. Hence the input resistance of a MOSFET is very high in the order of 1010 to 1015  $\Omega$ . The gate leakage current of a JFET is of the order of 10-9A., and its input resistance is of the order of 108 $\Omega$ .

- The output characteristics of the JFET are flatter than those of the MOSFET, and hence the drain resistance of a JFET (0.1 to  $1M\Omega$ ) is much higher than that of a MOSFET (1 to  $50k\Omega$ ).

- JFETs are operated only in the depletion mode. The depletion type MOSFET may be operated in both depletion and enhancement mode.

- Comparing to JFET, MOSFETs are easier to fabricate.

- Special digital CMOS circuits are available which involve near zero power dissipation and very low voltage and current requirements. This makes them suitable for portable systems.

# FET Amplifiers

### **INTRODUCTION**

•Field-effect transistors are three-terminal devices, but in contrast with the bipolar transistor, it is the voltage across two terminals that controls the current flowing in the third terminal. The three terminals in an FET are the *drain*, *source* and *gate*.

•Field Effect Transistor (FET) amplifiers provide an excellent voltage gain and high input impedence. Because of high input impedence and other characteristics of JFETs they are preferred over BJTs for certain types of applications.

•There are 3 basic FET circuit configurations:

i)Common Source

ii)Common Drain

iii)Common Gain

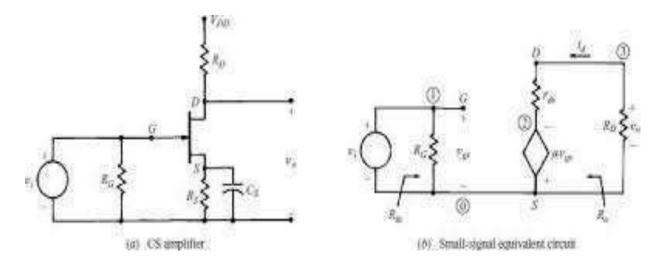

# Common Source (CS) Amplifier

A simple Common Source amplifier is shown in Fig. and associated small signal equivalent circuit using voltage-source model of FET is shown in Fig.

#### •Voltage Gain

Source resistance (RS) is used to set the Q-Point but is bypassed by CS for mid-frequency operation. From the small signal equivalent circuit, the output voltage

$VO = -RD\mu Vgs(RD + rd)$

Where Vgs = Vi, the input voltage,

Hence, the voltage gain,  $AV = VO / Vi = -RD\mu(RD + rd)$

#### •Input Impedence

From Input Impedence is Zi = RG

For voltage divider bias as in CE Amplifiers of BJT

$RG = R1 \parallel R2$

•Output Impedance: Output impedance is the impedance measured at the output terminals with the input voltage VI = 0

From the above when the input voltage Vi = 0, Vgs = 0 and hence  $\mu Vgs = 0$

The equivalent circuit for calculating output impedence is given in Fig. Output impedence  $Zo = rd \parallel RD$

Normally rd will be far greater than RD . Hence  $Zo \approx RD$

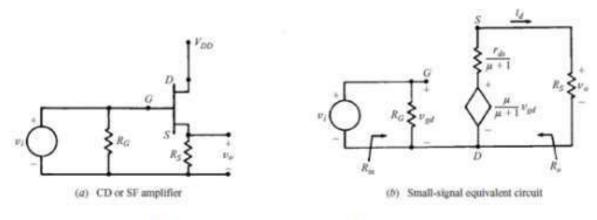

# Common Drain (CD) Amplifier

• A simple common drain amplifier is shown in Fig and associated small signal equivalent circuit using the voltage source model of FET is shown in Fig. Since voltage Vgd is more easily determined than Vgs, the voltage source in the output circuit is expressed in terms of Vgs and Thevenin's theorem

Fig. 7.2 (a)CD Amplifier (b)Small-signal equivalent circuit

Voltage Gain

The output voltage,

$VO = RS\mu Vgd / (\mu + 1) RS + rd$

Where Vgd = Vi the input voltage.

Hence, the voltage gain,  $Av = VO / Vi = RS\mu / (\mu + 1) RS + rd$ .

### • Input Impedence

From Fig , Input Impedence Zi = RG

### • Output Impedence

From Fig , Output impedence measured at the output terminals with input voltage Vi = 0 can be calculated from the following equivalent circuit.

As Vi = 0: Vgd = 0:  $\mu$ vgd / ( $\mu$  + 1) = 0 Output Impedence ZO = rd / ( $\mu$  + 1) || RS

When  $\mu \gg 1$

$ZO = (rd / \mu) \|RS = (1/gm)\|RS.$

# INTRODUCTION

- DIGITAL OPERATION OF A SYSTEM

- Digital systems are designed to store, process and communication information in digital form.

- A computer manipulates information in digital, are more precisely, binary form

- A binary number has only two descrete values zero or one.

- Each of these descete values is represented by the OFF and ON status of electronic switch called transitor.

# Why are binary number important

- We concentrate on binary numbers in this course

- Some convenation followed:

- Bit:single binary digit(0,1)

- Nibbble:collection of four bits

- Byte:collection of eight bits

- Word:collection of sixteen bits

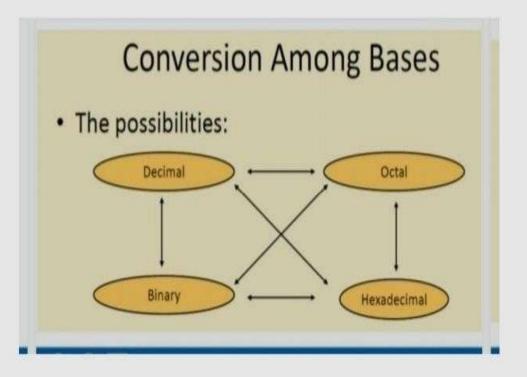

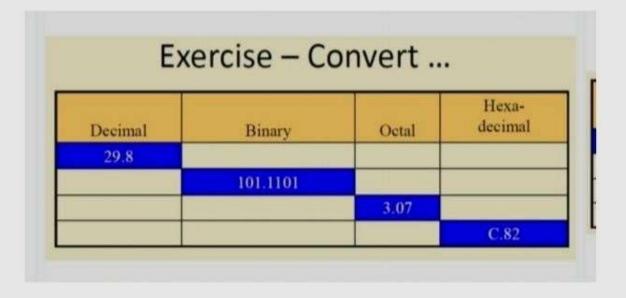

### Number system

| <ul> <li>Decimal</li> </ul> | Binary | Octal | Hexa decimal |

|-----------------------------|--------|-------|--------------|

| • 0.                        | 0      | 0.    | 0            |

| • 1.                        | 1.     | 1.    | 1            |

| • 2.                        | 10.    | 2.    | 2            |

| • 3.                        | 11.    | 3.    | 3            |

| • 4.                        | 100.   | 4.    | 4            |

| • 5.                        | 101.   | 5.    | 5            |

| • 6                         | 110.   | 6.    | 6            |

| • 7.                        | 111.   | 7     | 7            |

| • 8                         | 1000   | 10    | 8            |

| • 9                         | 1001   | 11.   | 9            |

12

and the second second

### Negative numbers

- 1. Sign and Magnitude Representation

- 2. 1's Complement Representation

- 3. 2's Complement Representation

- Goal of negative number systems

- Signed system: Simple. Just flip the sign bit

- 0 = positive

- 1 = negative

- One's complement: Replace subtraction with addition

- -Easy to derive (Just flip every bit)

- •Two's complement: Replace subtraction with addition

- -Addition of one's complement and one produces the

- two's complement.

3

### 1's complement:

- Formula: 2<sup>n</sup>-1 x

- i.e. n=4, 2<sup>4</sup> 1 x = 15 x

- In binary: (1 1 1 1) (b<sub>3</sub> b<sub>2</sub> b<sub>1</sub> b<sub>0</sub>)

- Just flip all the bits.

- 2's complement:

- Formula: 2<sup>n</sup>-x

- i.e. n=4, 2<sup>4</sup> x = 16 x

- In binary: (10000) (0 b<sub>3</sub> b<sub>2</sub> b<sub>1</sub> b<sub>0</sub>)

- Just flip all the bits and add 1.

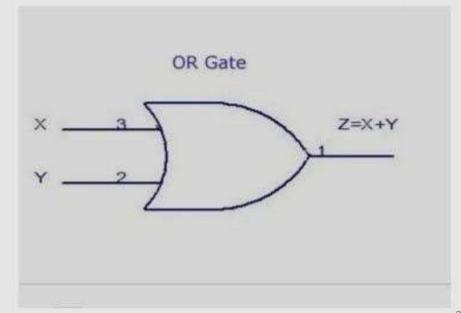

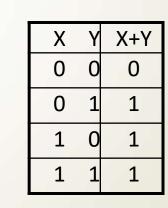

### OR Gate

Or gate is a digital logic gate that gives an output of 1 when any of its inputs are 1,otherwise 0

| 1                 | Truth table |                  |  |

|-------------------|-------------|------------------|--|

| Two Input OR gate |             |                  |  |

| Α                 | В           | <b>Y</b> = A + B |  |

| 0                 | 0           | 0                |  |

| 0                 | 1           | 1                |  |

| 1                 | 0           | 1                |  |

| 1                 | 1           | 1                |  |

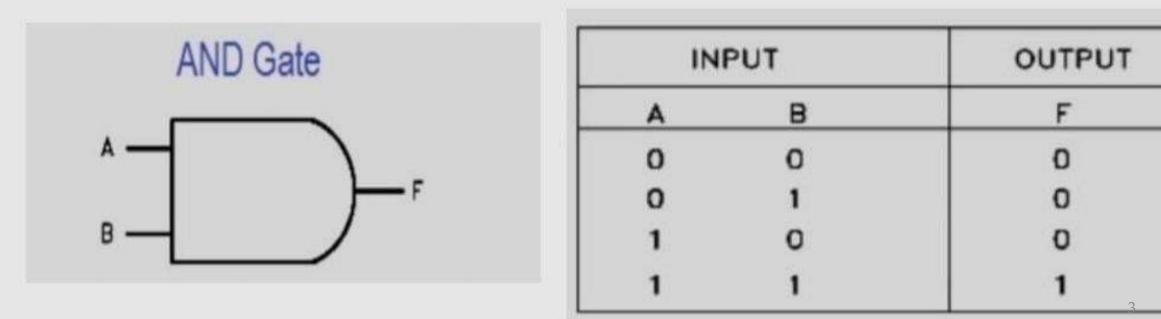

### AND Gate

The and gate is a basic digital logic gate that implement logical conjunction from mathemathical logic.

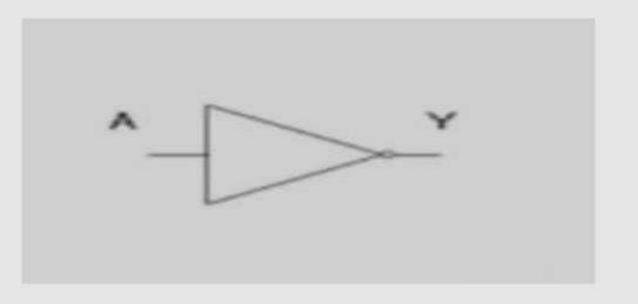

# NOT Gate

In digital logic an inveter or NOT gate is a logic gate which implement logical negation.

| Truth | Table |

|-------|-------|

| ^     | A.    |

| 1     | 0     |

| 0     | 1     |

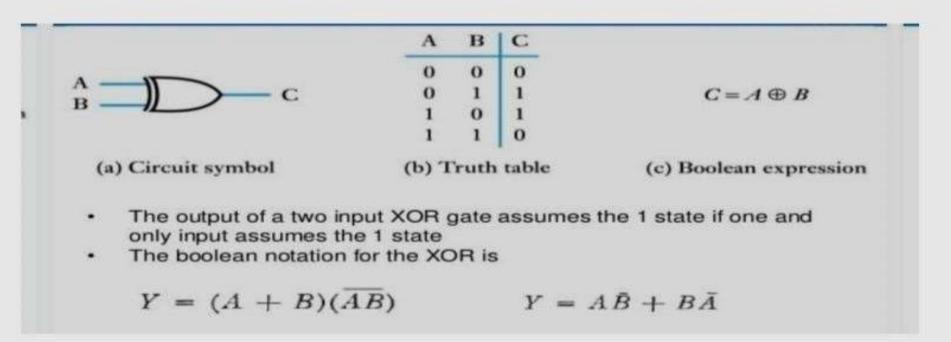

# EXCLUSIVE OR GATE

It is a digital logic gate that results in true eigher 1 or high. Output when the number of true inputs is an add count.

# DEMORGANS LAW

- The statement "if and only if all inputs are true(1), then the output is true(1)" is logically equivalent to the statement "If at least one input is false(0), then the output is false(0)"

- In boolean notation this equivalence can be written as

$$ABC \cdot \cdot \cdot = \overline{A} + \overline{B} + \overline{C} + \cdot \cdot \cdot$$

or

$$\overline{ABC \cdot \cdot \cdot} = \overline{A} + \overline{B} + \overline{C} + \cdot \cdot \cdot$$

$\overline{A + B + C + \cdots} = \overline{ABC} \cdots$  are known as De Morgan's laws

# LOGIC FAMILIES

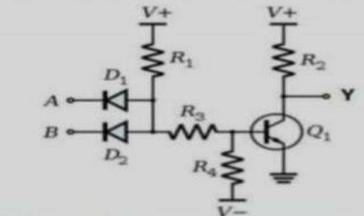

#### Diode transitor

- •DTL was first commercial available IC logic family in 53/73 series.

- The basic circuit in the DTL logic is the NAND gate.

- Each input associated with one diode.

- The diode and resistor form an AND gate.

- The transistor services as a NOT gate

| А | В | Y=A.B |

|---|---|-------|

| 0 | 0 | 1     |

| 0 | 1 | 1     |

| 1 | 0 | 1     |

| 1 | 1 | 0     |

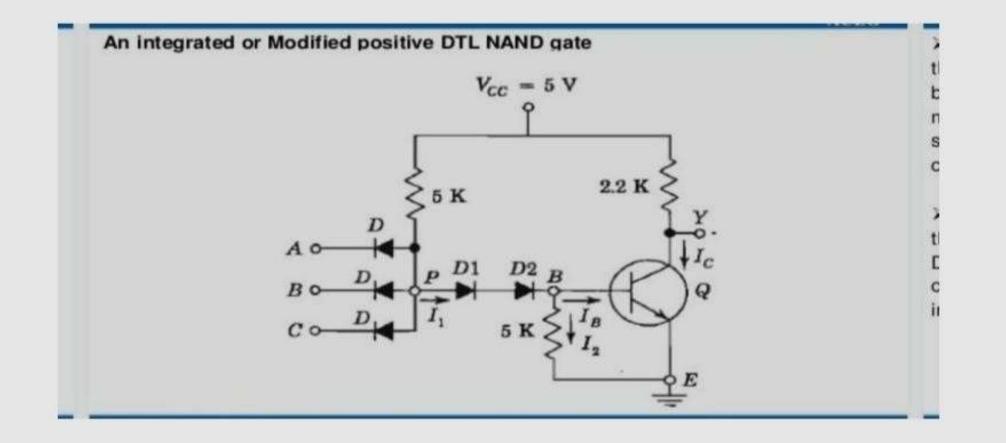

# MODIFIED DTL GATES

- Most logic gates are fabricated as an integrated circuit. In this all the transistors, diodes, resistors and capacitors in a fairly complicated circuit may be shaped within a tiny chip of single crystal silicon

- It turns out that large values of resistance and capacitance can not be fabricated economically

- ➢ In view of these facts the NAND gate is modified for integrated circuit implementation by eliminating the capacitor , reducing the resistance values drastically and using diodes or transistors to replace resistors wherever possible

# HIGH THRESHOULD LOGIC

➢In an Industrial environment the noise level is quite high because of the presence of motors, high voltage switches, on − off control circuits .....etc

➢By using a Zener diode in the place of diode D2 in the DTL gate this circuit is converted to the high noise immunity gate

# TRANSITOR TRANSITOR LOGIC

TTL family is modification to the DTL it has come to existence so has to over come speed limitation of DTL family

# TTL WORKING

The working of this circuit is identical to that of DTL circuit.

- Case1- When at least one input is logic LOW, transistor Q2 and Q3 are in cut-off and hence, output of Q3 is HIGH.

- Case2- When all inputs are HIGH, Q1 operates in active inverse mode, driving Q2 & Q3 in saturation. Since Q3 is ON, the output is LOW.

- Case3- While all inputs are HIGH, if any of the inputs suddenly goes LOW, then Q2 and Q3 will be turned off only when stored base charge is removed. The collector-base junction of Q1 is backbiased and Q1 operates in normal active region. A large collector current of Q1 is in such direction that it helps removing base charge of Q2 and Q3. In this way, the circuit speed is increased in TTL over speed of DTL.

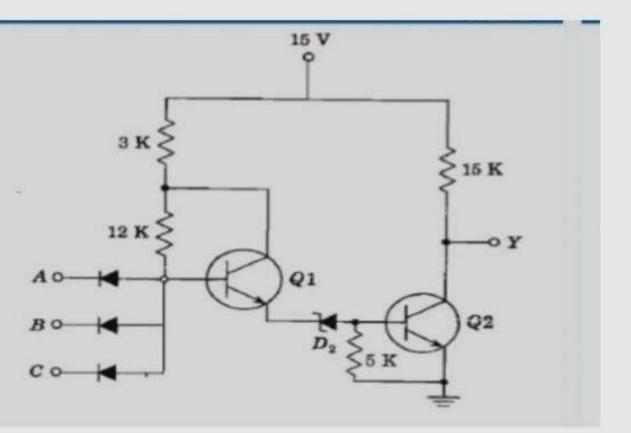

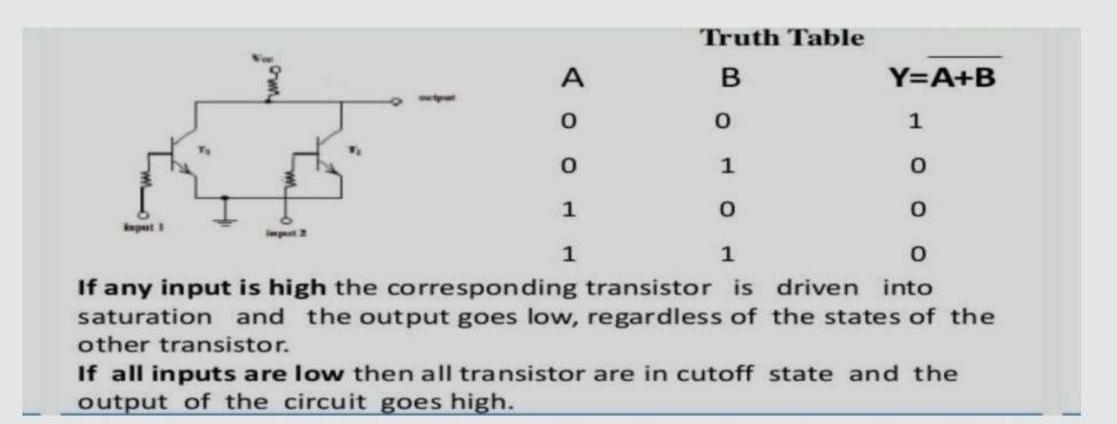

# RESISTOR TRANSISTOR LOGIC

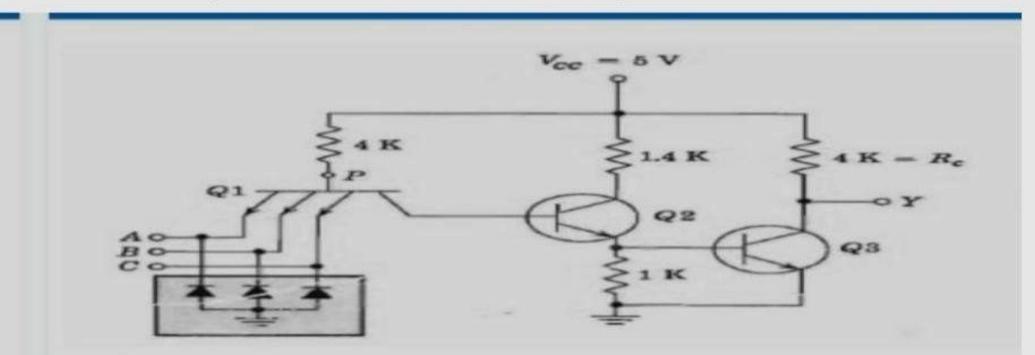

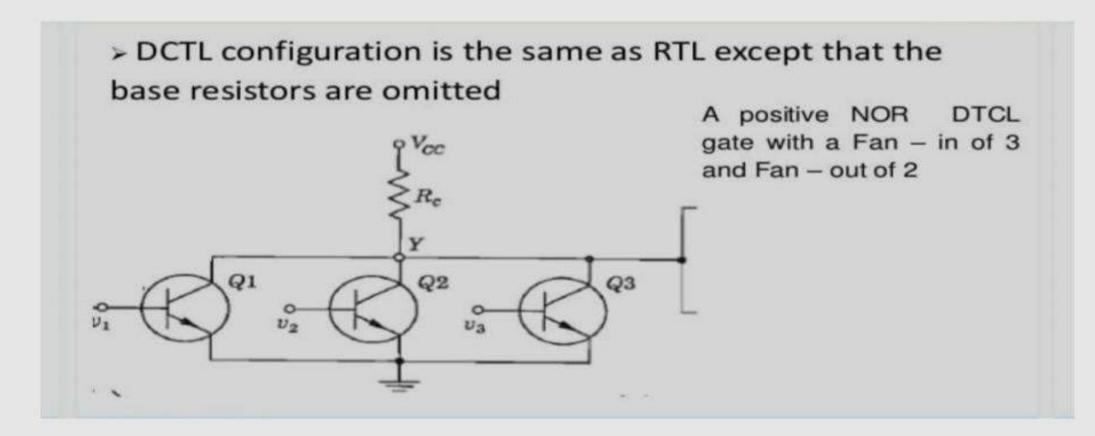

# DIRECT COUPLED TRANSISTOR LOGIC

# CMOS LOGIC FAMILY

➤T1 and T2 are n-channel MOSFETs while T3 and T4 are p-channel MOSFETs.

When both inputs A & B are HIGH, then T1 & T2 are ON while T3 & T4 are OFF. Hence, output is connected to GND i.e. LOW.

➤If either input is LOW, then either T3 or T4 is ON, connecting output is +Vcc i.e. HIGH.

| • | CMOS NOR gate     |                           |        |

|---|-------------------|---------------------------|--------|

|   | P <sup>+Vee</sup> | Similar is working of     | Р      |

| 3 |                   | CMOS NOR                  | В      |

| Ę | ''`]              | gate shown in figure      | F      |

| 1 |                   | aside. Here, p-channel    | N<br>P |

| , |                   | devices are in series and | CN     |

| , |                   | n-channel devices are in  | -      |

| C |                   | parallel.                 |        |

|   |                   |                           |        |

# COMPARISATION OF LOGIC FAMILY

|    | Parameter                      | RTL     | 12L                               | DTL            | HTL       | TTL            | ECL    | MOS    | CMOS           |

|----|--------------------------------|---------|-----------------------------------|----------------|-----------|----------------|--------|--------|----------------|

| 1. | Basic Gate                     | NOR     | NOR                               | NAND           | NAND      | NAND           | OR-NOR | NAND   | NOR or<br>NAND |

| 2. | Fan-out                        | 5       | Depends<br>on injector<br>current | 8              | 10        | 10<br>to<br>20 | 25     | 20     | 20<br>to<br>50 |

| з. | Power dissip-<br>ation in mW   | 12      | 6mm to 70<br>μM                   | 8-12           | 55        | 10             | .40-55 | 0.2-10 | 0.0025         |

| 4. | Noise<br>immunity              | Nominal | Poor                              | Good           | Excellent | Very<br>Good   | Poor   | Good   | Very<br>Good   |

| 5. | Propagation<br>delay (in sec.) | 12      | 25-250                            | 30             | 90        | 10             | 0.75   | 300    | 70.0           |

| 6. | Clock rate<br>(MHZ)            | 8       | -                                 | 72             | 4         | 35             | >60    | 2      | 10             |

| 7. | Available                      | High    | LSI<br>only                       | Fairty<br>high | Nominal   | Very<br>high   | High   | low    | High           |

# UNIT-4

# INTRODUCTION TO BOOLEAN ALGEBRA

# **BOOLEAN ALGEBRA**

- Also known as Switching Algebra

- Invented by mathematician George Boole in 1849

- Used by Claude Shannon at Bell Labs in 1938

- To describe digital circuits built from relays

- Digital circuit design is based on

- > Boolean Algebra

- Attributes

- Postulates

- Theorems

These allow minimization and manipulation of logic gates for optimizing digital circuits

# **BOOLEAN ALGEBRA ATTRIBUTES**

- Binary

- A1a: X=0 if X=1

- A1b: X=1 if X=0

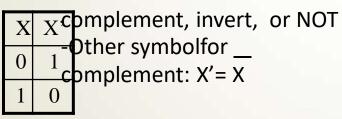

- Complement

- > aka invert, NOT

- A2a: if X=0, X'=1

- A2b: if X=1, X'=0

The tick mark ' means

- AND operation

- > A3a:0•0=0

- > A4a:1•1=1

- > A5a: 0•1=1•0=0

- The dot means AND

- Other symbol forAND: X•Y=XY (*no symbol*)

- The plus + means OR

- OR Operation

- > A3b:1+1=1

- > A4b:0+0=0

- > A5b: 1+0=0+1=1

X∙Y

0

0

0

Y

0

0

Х

0

0

1

1

# **BOOLEAN ALGEBRA ATTRIBUTES**

- Variable: Variables are the different symbols in a Boolean expression

- Literal: Each occurrence of a variable or its complement is called a literal

- Term: A term is the expression formed by literals and operations at one level

# $\overline{A} + A.B + A.\overline{C} + \overline{A}.B.C$

- A, B, C are three variables

- Eight Literals

- Expression has five terms including four AND terms and the OR term that combines the first-level AND terms.

## **BOOLEAN ALGEBRA POSTULATES**

#### **OR** operation

- Identity Elements

- > P2a: X+0=X

- > P2b: X•1=X

- > Cpganyutativity

- > P3b: X•Y=Y•X

- Complements

- > P6a: X+X'=1

- > P6b: X•X'=0

| Х | Y | X+0 | X+Y | Y+X | X | X+X′ |

|---|---|-----|-----|-----|---|------|

| 0 | 0 | 0   | 0   | 0   | 1 | 1    |

| 0 | 1 | 0   | 1   | 1   | 1 | 1    |

| 1 | 0 | 1   | 1   | 1   | 0 | 1    |

| 1 | 1 | 1   | 1   | 1   | 0 | 1    |

#### AND operation

| XY  | X•1 | X•Y | Y∙X | X' | X•X′ |

|-----|-----|-----|-----|----|------|

| 0 0 | 0   | 0   | 0   | 1  | 0    |

| 0 1 | 0   | 0   | 0   | 1  | 0    |

| 1 0 | 1   | 0   | 0   | 0  | 0    |

| 1 1 | 1   | 1   | 1   | 0  | 0    |

## **BOOLEAN ALGEBRA POSTULATES**

7

- Associativity

- > P4a: (X+Y)+Z=X+(Y+Z)

- > P4b: (X•Y)•Z=X•(Y•Z)

|   | X  | Y | Ζ | X+Y | (X+Y)+Z | Y+Z | X+(Y+Z) | X•Y | (X∙Y)∙Z | Y•Z | X∙(Y∙Z) |

|---|----|---|---|-----|---------|-----|---------|-----|---------|-----|---------|

| / | 0  | 0 | 0 | 0   | 0       | 0   | 0       | 0   | 0       | 0   | 0       |

|   | 0  | Ø | 1 | 0   | 1       | 1   | 1       | 0   | 0       | 0   | 0       |

|   | 9⁄ | 1 | 0 | 1   | 1       | 1   | 1       | 0   | 0       | 0   | 0       |

|   | 0  | 1 | 1 | 1   | 1       | 1   | 1       | 0   | 0       | 1   | 0       |

|   | 1  | 0 | 0 | 1   | 1       | 0   | 1       | 0   | 0       | 0   | 0       |

|   | 1  | 0 | 1 | 1   | 1       | 1   | 1       | 0   | 0       | 0   | 0       |

|   | 1  | 1 | 0 | 1   | 1       | 1   | 1       | 1   | 0       | 0   | 0       |

|   | 1  | 1 | 1 | 1   | 1       | 1   | 1       | 1   | 1       | 1   | 1       |

## **BOOLEAN ALGEBRA POSTULATES**

• Distributivity

- > P5a: X+(Y•Z) = (X+Y)•(X+Z)

- > P5b:  $X \bullet (Y+Z) = (X \bullet Y) + (X \bullet Z)$

|   | x  | Y | X+Y | X+Z | (X+Y)●<br>(X+Z) | Y•Z | X+<br>(Y∙Z) | X•Y | X•Z | X•Y+<br>X•Z | Y+Z | X•<br>(Y+Z) |

|---|----|---|-----|-----|-----------------|-----|-------------|-----|-----|-------------|-----|-------------|

| 0 | 0/ | Z | 0   | 0   | 0               | 0   | 0           | 0   | 0   | 0           | 0   | 0           |

| 0 | 0  | 1 | 0   | 1   | 0               | 0   | 0           | 0   | 0   | 0           | 1   | 0           |

| ø | 1  | 0 | 1   | 0   | 0               | 0   | 0           | 0   | 0   | 0           | 1   | 0           |

| 0 | 1  | 1 | 1   | 1   | 1               | 1   | 1           | 0   | 0   | 0           | 1   | 0           |

| 1 | 0  | 0 | 1   | 1   | 1               | 0   | 1           | 0   | 0   | 0           | 0   | 0           |

| 1 | 0  | 1 | 1   | 1   | 1               | 0   | 1           | 0   | 1   | 1           | 1   | 1           |

| 1 | 1  | 0 | 1   | 1   | 1               | 0   | 1           | 1   | 0   | 1           | 1   | 1           |

| 1 | 1  | 1 | 1   | 1   | 1               | 1   | 1           | 1   | 1   | 1           | 1   | 1           |

- Idempotency

- > T1a:X+X=X

- > T1b: X•X=X

- Null elements

- > T2a: X+1=1

- → T2b:X•0=0

- Involution

→ T3:(X')'=X

OR AND

| X | Υ | X+Y | X∙Y | X+X | X•X | X+1 | X•0 | X' | Χ" |

|---|---|-----|-----|-----|-----|-----|-----|----|----|

| 0 | 0 | 0   | 0   | 0   | 0   | 1   | 0   | 1  | 0  |

| 0 | 1 | 1   | 0   | 0   | 0   | 1   | 0   | 1  | 0  |

| 1 | 0 | 1   | 0   | 1   | 1   | 1   | 0   | 0  | 1  |

| 1 | 1 | 1   | 1   | 1   | 1   | 1   | 0   | 0  | 1  |

- Absorption (aka covering)

- → T4a: X+(X•Y)=X

- > T4b:  $X \bullet (X+Y)=X$

- > T5a: X+(X' Y)=X+Y

- > T5b: X●(X'+Y)=X●Y

OR AND

|   |   | X | X+Y | X•Y | X+<br>(X•Y) | X•<br>(X+Y) | X' | X'•Y | X+<br>(X'•Y) | X'+Y | X•<br>(X'+Y) |

|---|---|---|-----|-----|-------------|-------------|----|------|--------------|------|--------------|

|   |   | Y |     |     |             |             |    |      |              |      |              |

|   | 0 | 0 | 0   | 0   | 0           | 0           | 1  | 0    | 0            | 1    | 0            |

|   | 0 | 1 | 1   | 0   | 0           | 0           | 1  | 1    | 1            | 1    | 0            |

| I | 1 | 0 | 1   | 0   | 1           | 1           | 0  | 0    | 1            | 0    | 0            |

|   | 1 | 1 | 1   | 1   | 1           | 1           | 0  | 0    | 1            | 1    | 1            |

- Absorption (aka combining)

- → T6a: (X•Y)+(X•Y')=X

- > T6b: (X+Y)•(X+Y')=X

#### OR AND

| X |   | X+Y | X•Y | Y' | X•Y' | (X•Y)+<br>(X•Y') | X+Y' | (X+Y)•<br>(X+Y') |

|---|---|-----|-----|----|------|------------------|------|------------------|

| 0 | 0 | 0   | 0   | 1  | 0    | 0                | 1    | 0                |

| 0 | 1 | 1   | 0   | 0  | 0    | 0                | 0    | 0                |

| 1 | 0 | 1   | 0   | 1  | 1    | 1                | 1    | 1                |

| 1 | 1 | 1   | 1   | 0  | 0    | 1                | 1    | 1                |

- Absorption (aka *combining*)

- > T7a: (X•Y)+(X•Y'•Z)=(X•Y)+(X•Z)

- > T7b: (X+Y)•(X+Y'+Z) = (X+Y)•(X+Z)

| Γ |   |   |   |    |    |      | (XY)+  |    | (XY)+ |     | X+Y' | (X+Y)●   |     | (X+Y)● |

|---|---|---|---|----|----|------|--------|----|-------|-----|------|----------|-----|--------|

|   | Х | Y | Z | Υ' | XY | XY'Z | (XY'Z) | XZ | (XZ)  | X+Y | +Z   | (X+Y'+Z) | X+Z | (X+Z)  |

| Χ | 0 | 0 | 0 | 1  | 0  | 0    | 0      | 0  | 0     | 0   | 1    | 0        | 0   | 0      |

| ſ | 0 | 0 | 1 | 1  | 0  | 0    | 0      | 0  | 0     | 0   | 1    | 0        | 1   | 0      |

| ſ | 0 | 1 | 0 | 0  | 0  | 0    | 0      | 0  | 0     | 1   | 0    | 0        | 0   | 0      |

| Γ | 0 | 1 | 1 | 0  | 0  | 0    | 0      | 0  | 0     | 1   | 1    | 1        | 1   | 1      |

|   | 1 | 0 | 0 | 1  | 0  | 0    | 0      | 0  | 0     | 1   | 1    | 1        | 1   | 1      |

| ſ | 1 | 0 | 1 | 1  | 0  | 1    | 1      | 1  | 1     | 1   | 1    | 1        | 1   | 1      |

|   | 1 | 1 | 0 | 0  | 1  | 0    | 1      | 0  | 1     | 1   | 1    | 1        | 1   | 1      |

|   | 1 | 1 | 1 | 0  | 1  | 0    | 1      | 1  | 1     | 1   | 1    | 1        | 1   | 1      |

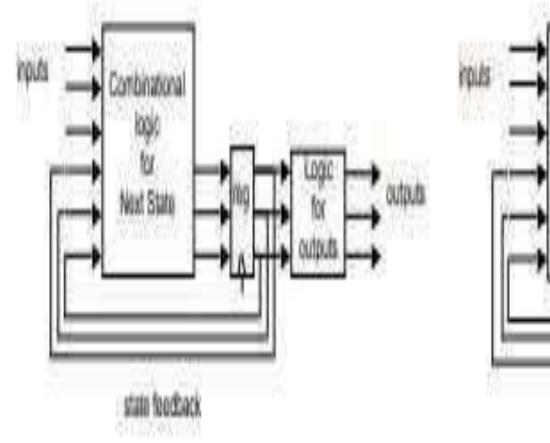

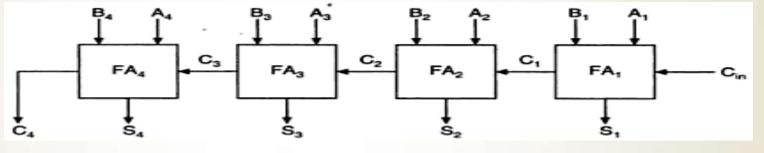

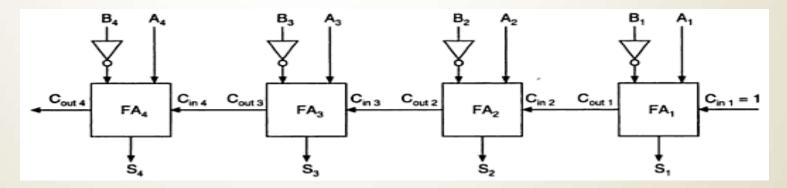

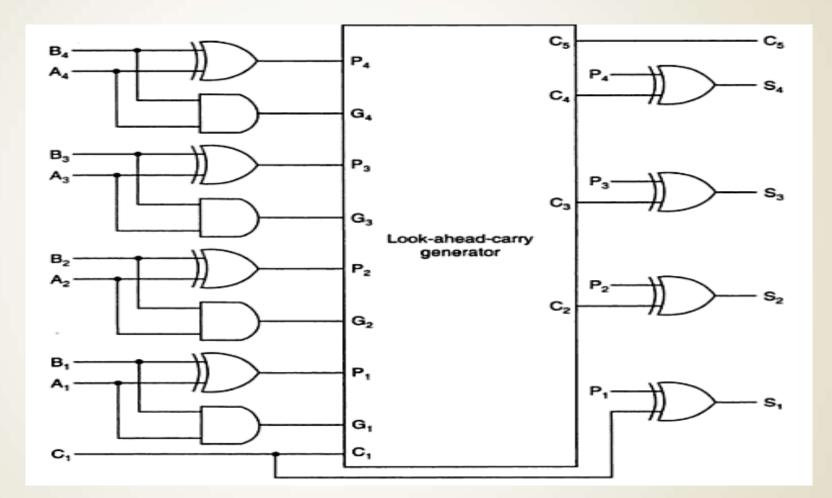

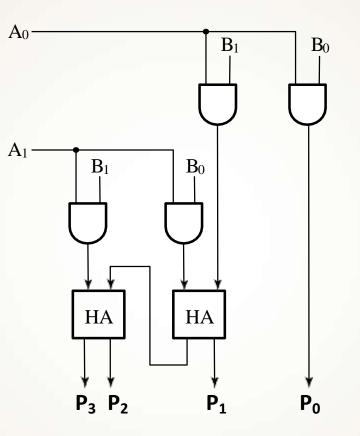

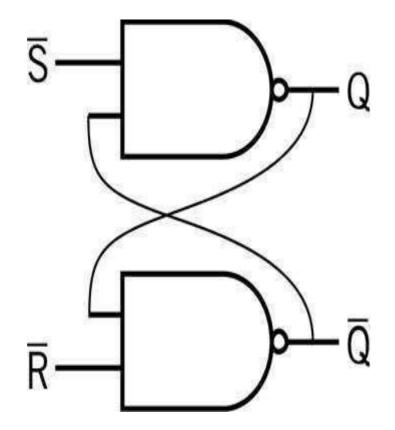

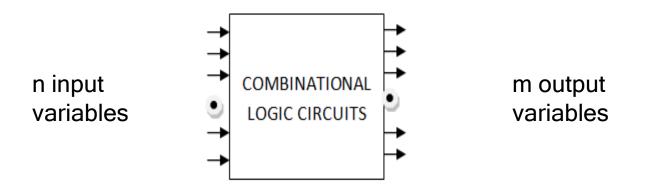

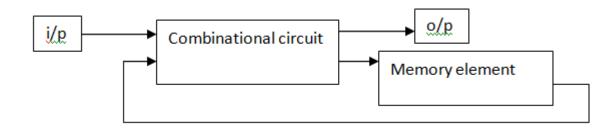

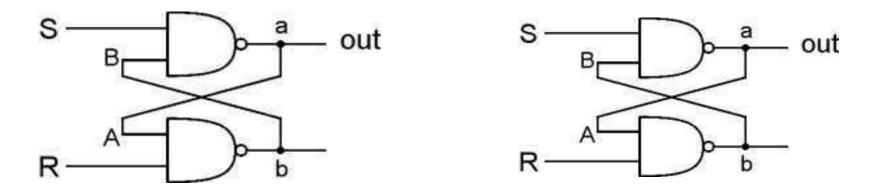

- DeMorgan's theorem (very important!)